Test: MOSFET Amplifier with CS Configuration - Electronics and Communication Engineering (ECE) MCQ

15 Questions MCQ Test - Test: MOSFET Amplifier with CS Configuration

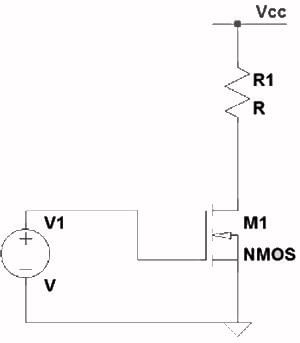

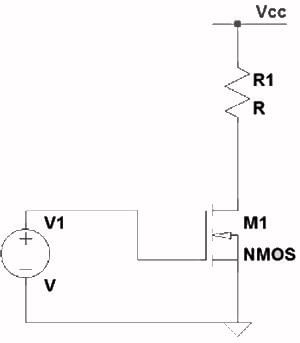

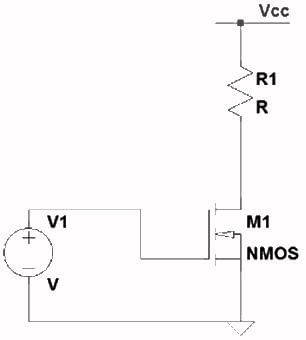

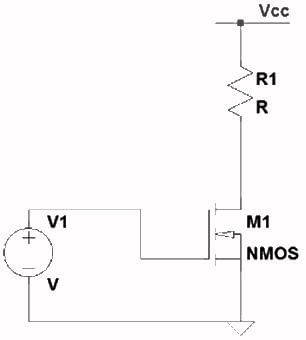

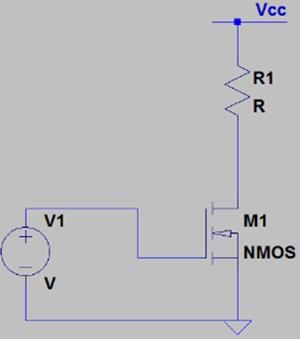

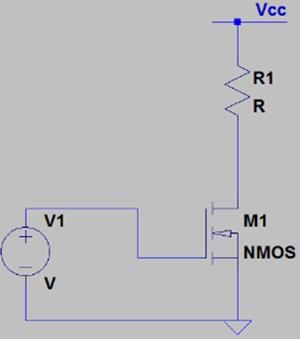

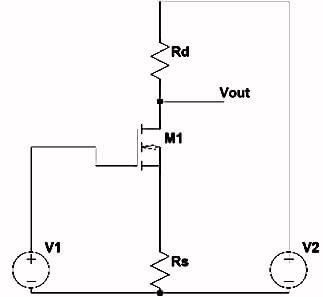

Neglecting Channel Length Modulation, what is the voltage gain from the gate to the drain of M1?

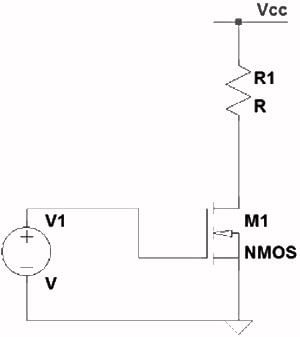

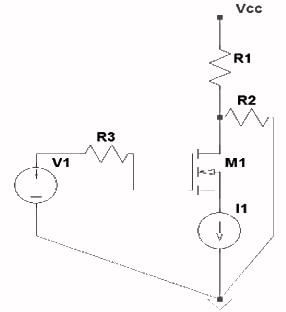

In the following C.S. stage shown below, what is the input impedance (ideally) if channel length modulation is neglected?

In the following C.S. stage shown below, what is the output impedance if λ > 0?

In the following C.S. stage shown below, what is the voltage gain from the gate to the drain of M1 if λ > 0?

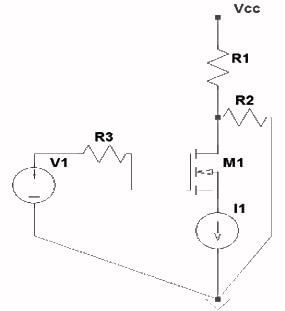

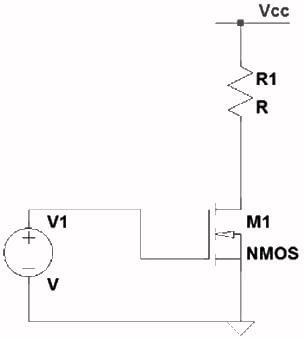

What is the overall input resistance of the CS stage shown below?

If the transconductance of M1 is 5S, voltage gain for the following degenerated CS stage is _____

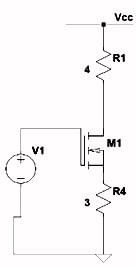

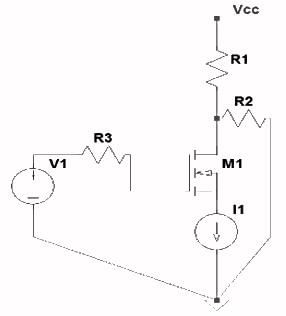

If both the MOSFET’s are identical and have channel length modulation, what is the output impedance at node S?

If Channel Length Modulation is present and gm is the transconductance of M1, what happens to the output resistance of for a fixed V2 in the following circuit?

In the following C.S. stage shown below, what is the transconductance?

In the following C.S. stage shown below, what is the input impedance if λ > 0?

In the following C.S. stage shown below, what is the output impedance, if channel length modulation is neglected?

If the output voltage is sensed at the collector, which of the following option perfectly describes the stage shown below?

If the output impedance of the current source is Ri, what is the output impedance of the CS stage shown below, if channel length modulation is neglected?

If both the MOSFET’s are identical, what is the voltage gain from V1 to node S?

If the internal resistance of the current source is finite, what will happen to the voltage gain. for the following C.S. stage, if K is doubled?

Hence, after putting the values, we get 5/4 and hence the answer becomes 1.25. Rd is the total resistance connected to the drain of the M1 while Rs is the total resistance connected to the source of the M1.

Hence, after putting the values, we get 5/4 and hence the answer becomes 1.25. Rd is the total resistance connected to the drain of the M1 while Rs is the total resistance connected to the source of the M1.

Both the currents enter node S and hence the voltage at node S is

Both the currents enter node S and hence the voltage at node S is  Cox (W/L) * (V1 - Vth)2.

Cox (W/L) * (V1 - Vth)2. , we find that a decrease in Rs leads to an increase in the voltage gain.

, we find that a decrease in Rs leads to an increase in the voltage gain.