Test: Pipelining Hazards - Computer Science Engineering (CSE) MCQ

10 Questions MCQ Test - Test: Pipelining Hazards

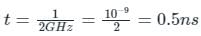

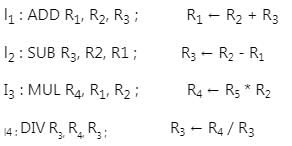

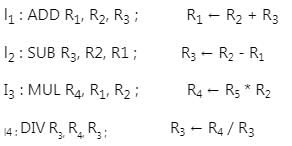

Consider a pipelined processor operating at 2 GHZ with 5 stages, Instruction fetch (IF), Instruction decode (ID), Execute (EX), Memory access (MEM), and write back (WB). Each stage of the pipeline, except the EX stage, takes one cycle. The EX takes one cycle for ADD and SUB, three cycles for MUL, two cycles for DIV Instruction.

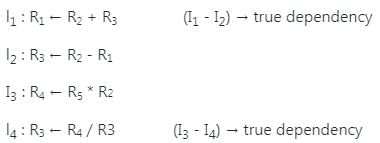

Consider the following instructions:

Find, the number of true data dependences in the above code and the execution time using operand forwarding technique respectively is______.

Find, the number of true data dependences in the above code and the execution time using operand forwarding technique respectively is______.

Which of the following hazards occurs when the pipeline makes the wrong decision on a branch prediction and therefore brings instructions into the pipeline that must subsequently be discarded?

Which of the following is NOT an instruction pipeline hazard ?

The locality of reference concept will fail in which of the following cases?

Where there are

If instruction X tries to modify some data before it is written by instruction (X-1), it can result in a ________ hazard.

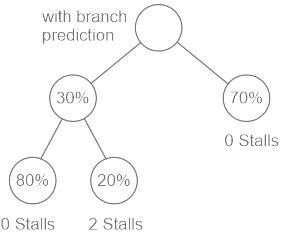

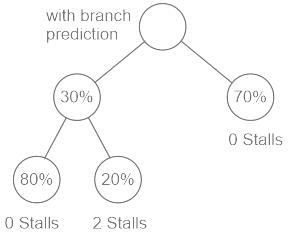

A processor X1 operating at 2 GHz has a standard 5-stage RISC instruction pipeline having a base CPI (cycles per instruction) of one without any pipeline hazards. For a given program P that has 30% branch instructions, control hazards incur 2 cycles stall for every branch. A new version of the processor X2 operating at same clock frequency has an additional branch predictor unit (BPU) that completely eliminates stalls for correctly predicted branches. There is neither any savings nor any additional stalls for wrong predictions. There are no structural hazards and data hazards for X1 and X2. If the BPU has a prediction accuracy of 80%, the speed up (rounded off to two decimal places) obtained by X2 over X1 in executing P is ______.

Which among the following is correct for the causes of pipeline conflict in pipelined processor?

(i) Resource

(ii) Data dependency

(iii) Branch difficulties

(iv) control dependency

One instruction tries to write an operand before it is written by previous instruction. This may lead to a dependency called

In the context of an instruction set, orthogonality indicates that other elements of an instruction are ______ of/by the opcode.

The method used for resolving data dependency conflict by the compiler itself is