GATE Mock Test Electronics Engineering (ECE)- 3 - Electronics and Communication Engineering (ECE) MCQ

30 Questions MCQ Test - GATE Mock Test Electronics Engineering (ECE)- 3

A vendor sells his articles at a certain profit percentage. If he sells his articles at 1/4th of his actual selling price then he incurs a loss of 60%. What is his actual profit percentage?

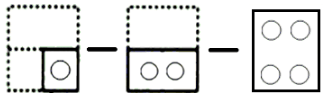

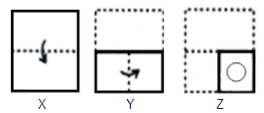

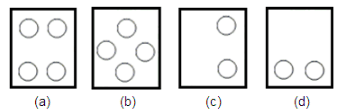

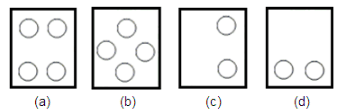

Directions: In the following question, a set of three figures X, Y and Z shows a sequence in which a piece of paper is folded and finally cut from one or more sections. Below these figures, a set of answer figures marked (a), (b), (c) and (d) shows the design which the paper actually acquires when it is unfolded. You have to select the answer figure which most closely resembles the unfolded piece of paper.

Criteria for selecting candidate for internship programme

The candidate:

can preferably start the internship between 18th Oct'17 and 17th Nov'17

are preferably available for duration of 6 months

have computer skills and interest in designing

have already graduated or are currently in any year of study

knows how to deal with customers Nick is a high school student and wants to do an internship as his summer project. He is a very vibrant boy and goes well with people.

Is he the right candidate for the internship?

can preferably start the internship between 18th Oct'17 and 17th Nov'17

are preferably available for duration of 6 months

have computer skills and interest in designing

have already graduated or are currently in any year of study

knows how to deal with customers Nick is a high school student and wants to do an internship as his summer project. He is a very vibrant boy and goes well with people.

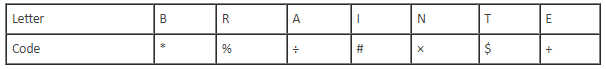

In a certain code, BRAIN is written as * % ÷ # x and TIER is written as $#+%. How is RENT written in that code?

Which of the following is MOST OPPOSITE in meaning to Locus?

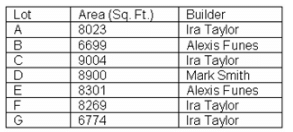

Directions: The table lists the size of building lots in the Orange Grove subdivision and the people who are planning to build on those lots. For each lot, installation of utilities costs $12,516. The city charges impact fees of $3,879 per lot. There are also development fees of 16.15 cents per square foot of land.

How much land does Mr. Taylor own in the Orange Grove subdivision?

The Union Sports Ministry has approved five lakh rupees from the National Welfare Fund for Sportspersons for Kaur Singh who is suffering from heart disease. Kaur Singh is associated with which of the following sports?

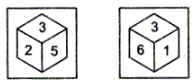

Two positions of a dice are given. Which of the following numbers would be at the top when 2 is at the bottom?

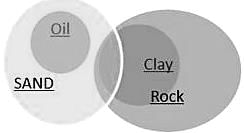

Direction: In given question below there are three statements followed by two conclusions numbered I and II. You have to take the given statements to be true even if they seem to be at variance with commonly known facts. Read all the conclusions and then decide which of the given conclusion logically follows from the given statements disregarding commonly known facts.

Statements:

All oils are sands

Some clays are oils

All clays are rocks

Conclusions:

- Atleast some clays are sands

- Some oil is not rock

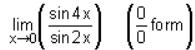

Walking at ![]() th of his usual speed, a man reaches his destination two minutes early. What is the time taken by him to cover the same distance at his usual speed?

th of his usual speed, a man reaches his destination two minutes early. What is the time taken by him to cover the same distance at his usual speed?

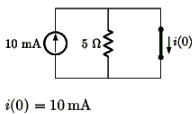

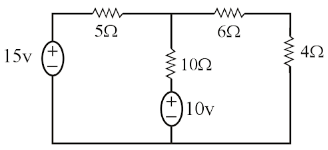

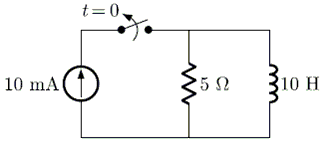

Given a network with values of components depicted in the figure.

Find the sum of current through 5Ω and 4Ω resistor.

Which of the following is correct?

Given the following system

T{X[n]} = X[n] + 3u[n+1]

Where u[x] represents unit step functions-

Which of the following is a correct representation of the system?

The width of the depletion layer is proportional to

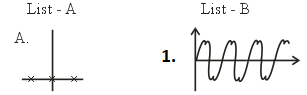

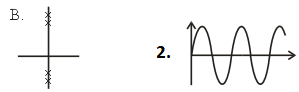

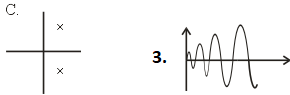

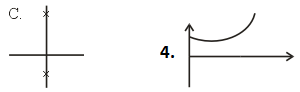

List-1 (pole location) with list-2(shown constant amplitude with impulse response).

Select the correct answer using the codes given below.

Which property is NOT considered in latches?

- Output of the latches changes as we change the input.

- changes as we change the input.

- Latches are edge triggered.

- Latches are fast.

In a PCM system, if the code word length is increased from 6 to 8 bits, the signal to quantization noise ratio improves by the factor

The far field of an antenna varies with distance r as

A semiconductor sample at room temperature has an intrinsic concentration of 2.5 X 1017 /m3. After doping what will be the minority carrier concentration if the majority carrier concentration is given as 5.5 X 1021 /m3.

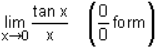

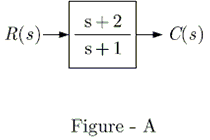

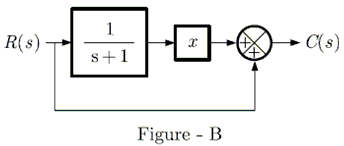

If the block diagram shown in figure 'A' and figure 'B' are equivalent, then x in figure 'B' will be equal to

For an ideal p-channel MOSFET, μp= 300cm2/v-s, W = 15μm, L = 1.5μm, tox = 300A, Vt = -0.7V. If the transistor is non-saturation region at VSD=0.5V, then what is the Transconductance gm?

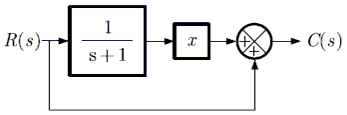

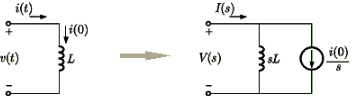

Which of the following is/are s-domain equivalent of the circuit shown below?

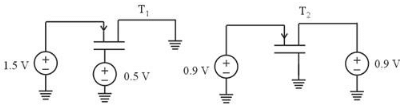

From the circuit given below, find out the operating region of the transistors T1 and T2

(VTH = -0.4)

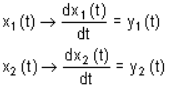

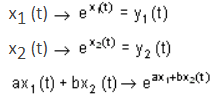

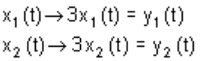

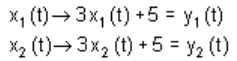

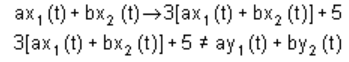

Consider the following CT systems with an input x(t) and output y(t).

System P : y(t) = dx(t)/dt

System Q : y(t) = ex(t)

System R : y(t) = 3x(t)

System S : y(t) = 3x(t) + 5

Which of the above system is/are linear?

A communication channel having AWGN characteristics is operating in such a way that SNR >> 1. The bandwidth of signal being transmitted is B and capacity C1. Determine the capacity of channel if a signal with half the bandwidth is transmitted through the same channel with same quality.

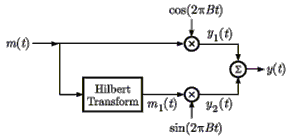

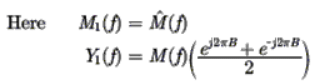

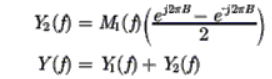

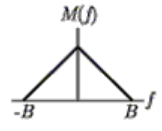

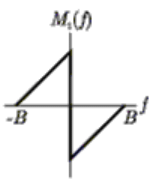

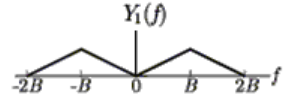

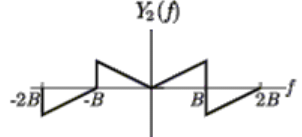

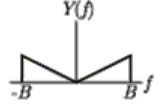

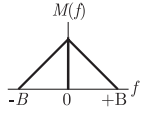

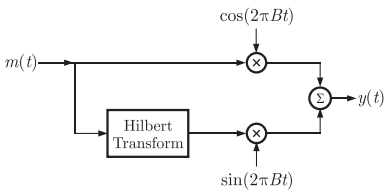

In the following scheme, if the spectrum M(f) of m(t) is as shown, then the spectrum Y(f) of y(t) will be

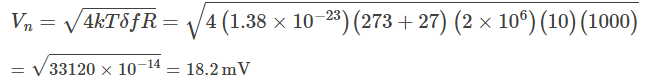

An amplifier operating over the frequency range of 18 to 20 MHz has a 10kΩ input resistance.The RMS noise voltage at the input to the amplifier at ambient temperature is (assume Boltzman’s constant = 1.38 × 10−23J/K)

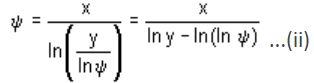

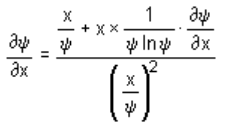

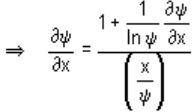

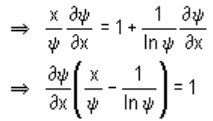

Consider two functions x = ψ ln Φ and y =Φ In ψ . Which of the following is the correct expression for ∂ψ/∂x ?

What is the maximum torque (in Nm) on a square loop of 200 turns in a field of uniform flux density of 1 Wb/m2. The loop has 15cm side and carries a current of 5A.

The sampling rate for Compact Discs (CDs) is 44,000 samples/s. If the samples are quantized to 256 levels and binary coded, the corresponding bit rate (in bits per second) is ______.(Answer up to the nearest integer)