All Exams >

Electronics and Communication Engineering (ECE) >

Digital Circuits >

All Questions

All questions of Machine Instructions & Addressing Modes for Electronics and Communication Engineering (ECE) Exam

Which of the following statements is/are true?- a)Parallelism is high in horizontal microprogrammed control unit as compared to vertical microprogrammed control unit.

- b)Hardwired control unit is slower compared to microprogrammed control unit.

- c)In 2’s complement sum carry flag and overflow are the same

- d)In 2’s complement sum if the sum of two negative numbers yields a positive result, the sum has overflowed

Correct answer is option 'A,D'. Can you explain this answer?

Which of the following statements is/are true?

a)

Parallelism is high in horizontal microprogrammed control unit as compared to vertical microprogrammed control unit.

b)

Hardwired control unit is slower compared to microprogrammed control unit.

c)

In 2’s complement sum carry flag and overflow are the same

d)

In 2’s complement sum if the sum of two negative numbers yields a positive result, the sum has overflowed

|

Vertex Academy answered |

Option 1: Parallelism is high in the horizontal microprogrammed control unit as compared to a vertical microprogrammed control unit.

True, Parallelism is high in horizontal microprogramming as several operations on different registers can be performed simultaneously.

True, Parallelism is high in horizontal microprogramming as several operations on different registers can be performed simultaneously.

Option 2: Hardwired control unit is slower compared to the microprogrammed control unit.

False, a Hardwired control unit is faster as compared to the microprogrammed control unit as there won’t be a delay of fetch, decoding, and executing the control instructions in the case of the hardwired control unit.

False, a Hardwired control unit is faster as compared to the microprogrammed control unit as there won’t be a delay of fetch, decoding, and executing the control instructions in the case of the hardwired control unit.

Option 3: In 2’s complement sum carry flag and overflow are the same.

False, In unsigned numbers, carry out is equivalent to overflow. But in two's complement, carry out tells you nothing about overflow.

False, In unsigned numbers, carry out is equivalent to overflow. But in two's complement, carry out tells you nothing about overflow.

Option 4: In 2’s complement sum if the sum of two negative numbers yields a positive result, the sum has overflowed.

True, the Following are the rules for detecting overflow in a two's complement sum:

True, the Following are the rules for detecting overflow in a two's complement sum:

- If the sum of two positive numbers yields a negative result, the sum has overflowed.

- If the sum of two negative numbers yields a positive result, the sum has overflowed.

Otherwise, the sum has not overflowed.

Hence the correct answer is option 1 and option 4.

Hence the correct answer is option 1 and option 4.

In X = (M + N × O) / (P × Q), how many one-address instructions are required to evaluate it?- a)4

- b)6

- c)8

- d)10

Correct answer is option 'C'. Can you explain this answer?

In X = (M + N × O) / (P × Q), how many one-address instructions are required to evaluate it?

a)

4

b)

6

c)

8

d)

10

|

|

Sudhir Patel answered |

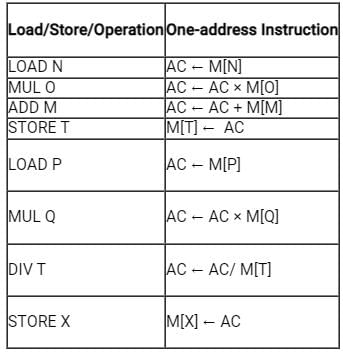

All the operations will be performed in the Accumulator register(AC).

The load operation is used to fetch the value from register or memory to accumulator.

The store operation is used to store the value from the accumulator to register or memory.

The one address instructions for the given equations are:

The load operation is used to fetch the value from register or memory to accumulator.

The store operation is used to store the value from the accumulator to register or memory.

The one address instructions for the given equations are:

Hence, the correct answer is "option 3".

A CPU has 12 registers and uses 6 addressing modes. RAM is 64K × 32. What is the maximum size of the op-code field if the instruction has a register operand and a memory address operand?- a)8 bits

- b)9 bits

- c)10 bits

- d)11 bits

Correct answer is option 'B'. Can you explain this answer?

A CPU has 12 registers and uses 6 addressing modes. RAM is 64K × 32. What is the maximum size of the op-code field if the instruction has a register operand and a memory address operand?

a)

8 bits

b)

9 bits

c)

10 bits

d)

11 bits

|

|

Nayanika Deshpande answered |

A CPU with 12 registers means that it has 12 small storage units (registers) that can hold data. These registers are used for storing and manipulating data during processing.

The 6 addressing modes refer to the different ways in which the CPU can access data from RAM (Random Access Memory). These addressing modes determine how the CPU calculates the memory address of the data it wants to access.

The RAM size of 64K means that the CPU can access a maximum of 64 kilobytes (or 64,000 bytes) of data from the RAM. This memory is used for storing data and instructions that the CPU needs to execute.

Overall, these specifications provide information about the capabilities of the CPU in terms of data storage and access. The number of registers and addressing modes determine the efficiency and flexibility of the CPU in performing computations and accessing data, while the RAM size determines the amount of data that can be stored and accessed by the CPU.

The 6 addressing modes refer to the different ways in which the CPU can access data from RAM (Random Access Memory). These addressing modes determine how the CPU calculates the memory address of the data it wants to access.

The RAM size of 64K means that the CPU can access a maximum of 64 kilobytes (or 64,000 bytes) of data from the RAM. This memory is used for storing data and instructions that the CPU needs to execute.

Overall, these specifications provide information about the capabilities of the CPU in terms of data storage and access. The number of registers and addressing modes determine the efficiency and flexibility of the CPU in performing computations and accessing data, while the RAM size determines the amount of data that can be stored and accessed by the CPU.

RISC stands for:- a)Remaining Instruction Set of Computer

- b)Remaining Intermediate Storage of Computer

- c)Reduced Intermediate Storage of Computer

- d)Reduced Instruction Set Computer

Correct answer is option 'D'. Can you explain this answer?

RISC stands for:

a)

Remaining Instruction Set of Computer

b)

Remaining Intermediate Storage of Computer

c)

Reduced Intermediate Storage of Computer

d)

Reduced Instruction Set Computer

|

|

Sudhir Patel answered |

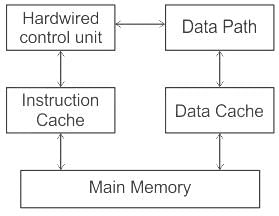

RISC is implemented using hardwire control unit. RISC uses registers instead of memory. Registers are small in size and are on the same chip on which ALU and control unit are present. RISC architecture is shown below.

Feature of RISC processor are:

- RISC instruction set are simple and of fix size.

- Fewer instructions in RISC.

- High performance

- Simple addressing modes

- Large number of registers.

- Instruction come under size of one word.

Which of the following statements is/are true?- a)In the immediate addressing mode the operand is placed in the instruction itself

- b)One byte machine instruction consists of only operand

- c)Indirect addressing mode is suitable for implementing pointers in C

- d)Displacement addressing mode is similar to the register indirect addressing mod

Correct answer is option 'A,C,D'. Can you explain this answer?

Which of the following statements is/are true?

a)

In the immediate addressing mode the operand is placed in the instruction itself

b)

One byte machine instruction consists of only operand

c)

Indirect addressing mode is suitable for implementing pointers in C

d)

Displacement addressing mode is similar to the register indirect addressing mod

|

|

Arnab Desai answered |

Statement a) In the immediate addressing mode the operand is placed in the instruction itself

In immediate addressing mode, the operand is directly specified within the instruction itself. This means that the value of the operand is not stored in a memory location or a register, but rather it is included as a part of the instruction. This is useful when a constant value or literal is needed as an operand. For example, in the instruction "ADD R1, #5", the value 5 is directly specified in the instruction itself.

Statement c) Indirect addressing mode is suitable for implementing pointers in C

Indirect addressing mode is a mode of addressing in which the operand is the address of a memory location that contains the actual value to be used. This mode is commonly used for implementing pointers in programming languages like C, where a pointer variable holds the memory address of another variable. By using indirect addressing mode, the value of the pointer variable can be used to access the value stored at the memory location it points to. This allows for dynamic memory allocation and manipulation, which is a key feature in C programming.

Statement d) Displacement addressing mode is similar to the register indirect addressing mode

Displacement addressing mode is a mode of addressing in which the operand is the sum of a base address and a constant displacement. The base address is typically stored in a register, and the displacement value is specified as a constant value within the instruction. This mode is commonly used in assembly language programming to access elements of arrays or structures. It is similar to register indirect addressing mode in that both modes involve accessing memory locations based on a computed address. However, in displacement addressing mode, the computed address is the sum of a base address and a constant displacement, whereas in register indirect addressing mode, the computed address is stored in a register.

To sum up, the true statements are:

a) In the immediate addressing mode, the operand is placed in the instruction itself.

c) Indirect addressing mode is suitable for implementing pointers in C.

d) Displacement addressing mode is similar to the register indirect addressing mode.

In immediate addressing mode, the operand is directly specified within the instruction itself. This means that the value of the operand is not stored in a memory location or a register, but rather it is included as a part of the instruction. This is useful when a constant value or literal is needed as an operand. For example, in the instruction "ADD R1, #5", the value 5 is directly specified in the instruction itself.

Statement c) Indirect addressing mode is suitable for implementing pointers in C

Indirect addressing mode is a mode of addressing in which the operand is the address of a memory location that contains the actual value to be used. This mode is commonly used for implementing pointers in programming languages like C, where a pointer variable holds the memory address of another variable. By using indirect addressing mode, the value of the pointer variable can be used to access the value stored at the memory location it points to. This allows for dynamic memory allocation and manipulation, which is a key feature in C programming.

Statement d) Displacement addressing mode is similar to the register indirect addressing mode

Displacement addressing mode is a mode of addressing in which the operand is the sum of a base address and a constant displacement. The base address is typically stored in a register, and the displacement value is specified as a constant value within the instruction. This mode is commonly used in assembly language programming to access elements of arrays or structures. It is similar to register indirect addressing mode in that both modes involve accessing memory locations based on a computed address. However, in displacement addressing mode, the computed address is the sum of a base address and a constant displacement, whereas in register indirect addressing mode, the computed address is stored in a register.

To sum up, the true statements are:

a) In the immediate addressing mode, the operand is placed in the instruction itself.

c) Indirect addressing mode is suitable for implementing pointers in C.

d) Displacement addressing mode is similar to the register indirect addressing mode.

A processor has 300 distinct instructions and 70 general-purpose registers. A 32-bit instruction word has an opcode, two register operands, and an immediate operand. The number of bits available for the immediate operand field is_____

Correct answer is '9'. Can you explain this answer?

A processor has 300 distinct instructions and 70 general-purpose registers. A 32-bit instruction word has an opcode, two register operands, and an immediate operand. The number of bits available for the immediate operand field is_____

|

|

Devika Gupta answered |

Given Information:

- The processor has 300 distinct instructions.

- The processor has 70 general-purpose registers.

- A 32-bit instruction word has an opcode, two register operands, and an immediate operand.

To find:

The number of bits available for the immediate operand field.

Solution:

Since we know that a 32-bit instruction word has an opcode, two register operands, and an immediate operand, we can calculate the number of bits available for the immediate operand field using the following steps:

Step 1: Calculate the number of bits required for the opcode.

Since the processor has 300 distinct instructions, we need to represent each instruction with a unique opcode. The number of bits required to represent 300 distinct instructions is given by:

Number of bits for opcode = ceil(log2(300))

Step 2: Calculate the number of bits required for the register operands.

Since the processor has 70 general-purpose registers, we need to represent two register operands in the instruction word. The number of bits required to represent 70 registers is given by:

Number of bits for register operands = ceil(log2(70))

Step 3: Calculate the number of bits available for the immediate operand field.

The total number of bits used by the opcode and register operands can be calculated by adding the number of bits required for the opcode and register operands:

Total number of bits used = Number of bits for opcode + Number of bits for register operands

Since we know that the instruction word is 32 bits in total, the number of bits available for the immediate operand field can be calculated by subtracting the total number of bits used from 32:

Number of bits available for immediate operand field = 32 - Total number of bits used

Therefore, the final answer is 9 bits.

- The processor has 300 distinct instructions.

- The processor has 70 general-purpose registers.

- A 32-bit instruction word has an opcode, two register operands, and an immediate operand.

To find:

The number of bits available for the immediate operand field.

Solution:

Since we know that a 32-bit instruction word has an opcode, two register operands, and an immediate operand, we can calculate the number of bits available for the immediate operand field using the following steps:

Step 1: Calculate the number of bits required for the opcode.

Since the processor has 300 distinct instructions, we need to represent each instruction with a unique opcode. The number of bits required to represent 300 distinct instructions is given by:

Number of bits for opcode = ceil(log2(300))

Step 2: Calculate the number of bits required for the register operands.

Since the processor has 70 general-purpose registers, we need to represent two register operands in the instruction word. The number of bits required to represent 70 registers is given by:

Number of bits for register operands = ceil(log2(70))

Step 3: Calculate the number of bits available for the immediate operand field.

The total number of bits used by the opcode and register operands can be calculated by adding the number of bits required for the opcode and register operands:

Total number of bits used = Number of bits for opcode + Number of bits for register operands

Since we know that the instruction word is 32 bits in total, the number of bits available for the immediate operand field can be calculated by subtracting the total number of bits used from 32:

Number of bits available for immediate operand field = 32 - Total number of bits used

Therefore, the final answer is 9 bits.

Only instructions with zero, one, and two addresses are supported by some CPUs. The size of an op-code is 16 bits, whereas the size of an address is 4 bits.What is the Maximum number of two address instructions?

Correct answer is '256'. Can you explain this answer?

Only instructions with zero, one, and two addresses are supported by some CPUs. The size of an op-code is 16 bits, whereas the size of an address is 4 bits.

What is the Maximum number of two address instructions?

|

|

Sagnik Desai answered |

The Maximum Number of Two-Address Instructions

In order to determine the maximum number of two-address instructions, we need to consider the size of the op-code and the size of the address.

Size of Op-code

The size of the op-code is given as 16 bits. This means that the op-code can have 2^16 = 65536 different values.

Size of Address

The size of the address is given as 4 bits. This means that the address can have 2^4 = 16 different values.

Two-Address Instructions

A two-address instruction is an instruction that operates on two operands and requires two addresses. In this case, the instruction format would typically include two fields for the addresses of the operands.

Calculating the Maximum Number of Two-Address Instructions

To calculate the maximum number of two-address instructions, we need to consider the number of possible combinations of op-code and address fields.

Number of Possible Op-code Values

As mentioned earlier, the op-code can have 65536 different values.

Number of Possible Address Combinations

Since the address field has 4 bits, it can have 16 different values. For each operand, we have 16 possible values, giving us a total of 16 * 16 = 256 possible combinations of addresses.

Total Number of Two-Address Instructions

To calculate the total number of two-address instructions, we multiply the number of possible op-code values by the number of possible address combinations.

Total Number of Two-Address Instructions = Number of Op-code Values * Number of Address Combinations

= 65536 * 256

= 16777216

Conclusion

The maximum number of two-address instructions is 16777216. However, since the size of the op-code is 16 bits and the size of the address is 4 bits, only instructions with zero, one, and two addresses are supported by some CPUs. Therefore, the maximum number of two-address instructions is limited to the number of possible address combinations, which is 256.

In order to determine the maximum number of two-address instructions, we need to consider the size of the op-code and the size of the address.

Size of Op-code

The size of the op-code is given as 16 bits. This means that the op-code can have 2^16 = 65536 different values.

Size of Address

The size of the address is given as 4 bits. This means that the address can have 2^4 = 16 different values.

Two-Address Instructions

A two-address instruction is an instruction that operates on two operands and requires two addresses. In this case, the instruction format would typically include two fields for the addresses of the operands.

Calculating the Maximum Number of Two-Address Instructions

To calculate the maximum number of two-address instructions, we need to consider the number of possible combinations of op-code and address fields.

Number of Possible Op-code Values

As mentioned earlier, the op-code can have 65536 different values.

Number of Possible Address Combinations

Since the address field has 4 bits, it can have 16 different values. For each operand, we have 16 possible values, giving us a total of 16 * 16 = 256 possible combinations of addresses.

Total Number of Two-Address Instructions

To calculate the total number of two-address instructions, we multiply the number of possible op-code values by the number of possible address combinations.

Total Number of Two-Address Instructions = Number of Op-code Values * Number of Address Combinations

= 65536 * 256

= 16777216

Conclusion

The maximum number of two-address instructions is 16777216. However, since the size of the op-code is 16 bits and the size of the address is 4 bits, only instructions with zero, one, and two addresses are supported by some CPUs. Therefore, the maximum number of two-address instructions is limited to the number of possible address combinations, which is 256.

In 8051, the accumulator register contains 80H and B register contains 8FH. The content of the accumulator and status of the carry flag after the addition operation are respectively- a)0FH, 1

- b)10FH, 0

- c)FFH, 1

- d)10FH, 1

Correct answer is option 'A'. Can you explain this answer?

In 8051, the accumulator register contains 80H and B register contains 8FH. The content of the accumulator and status of the carry flag after the addition operation are respectively

a)

0FH, 1

b)

10FH, 0

c)

FFH, 1

d)

10FH, 1

|

Vertex Academy answered |

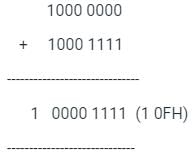

A= 80H

B= 8FH

[A] + [B] = 80H + 8FH = 1 0FH

B= 8FH

[A] + [B] = 80H + 8FH = 1 0FH

But accumulator is an 8-bit register

Accumulator = 0FH

carry flag= 1

Hence the correct answer is 0FH, 1.

Which one of the following is a special characteristic of RISC processor?- a)Provide direct manipulation of operands residing in memory

- b)A large variety of addressing modes

- c)Variable length instruction formats

- d)Overlapped register window

Correct answer is option 'D'. Can you explain this answer?

Which one of the following is a special characteristic of RISC processor?

a)

Provide direct manipulation of operands residing in memory

b)

A large variety of addressing modes

c)

Variable length instruction formats

d)

Overlapped register window

|

Vertex Academy answered |

RISC means Reduced Instruction Set as the acronym says aims to reduce the execution times of instructions by simplifying the instructions.

The major characteristics of RISC are as follows:

The major characteristics of RISC are as follows:

- Compared to normal instructions they have a lower number of instructions.

- The addressing modes in the case of RISC are also lower.

- All the operations that are required to be performed take place within the CPU.

- All instructions are executed in a single cycle and hence have a faster execution time.

- The characteristic of some RISC CPUs is to use an overlapped register window that provides the passing of parameters to called procedure and stores the result to the calling procedure.

- In this architecture, the processors have a large number of registers and a much more efficient instruction pipeline.

- Also, the instruction formats are of fixed length and can be easily decoded.

The following language uses mnemonic OP codes- a)Assembly language

- b)High level language

- c)BASIC language

- d)Machine language

Correct answer is option 'A'. Can you explain this answer?

The following language uses mnemonic OP codes

a)

Assembly language

b)

High level language

c)

BASIC language

d)

Machine language

|

|

Akash Rane answered |

Assembly Language

Assembly language is a low-level programming language that uses mnemonic opcode instructions. It is a human-readable representation of machine language instructions. In assembly language, each mnemonic opcode represents a specific machine instruction that can be directly executed by the computer's hardware.

Explanation:

Assembly language is a programming language that provides a one-to-one correspondence between the instructions executed by a computer's central processing unit (CPU) and the mnemonic codes used to represent those instructions. It is considered a low-level language because it closely resembles the binary machine language of the computer.

Assembly language is specific to a particular computer architecture and is often used for tasks that require direct hardware manipulation or for optimizing performance. It provides a level of abstraction above machine language, making it easier for programmers to read and write code.

Key Points:

- Assembly language uses mnemonic opcode instructions.

- Mnemonic opcodes are human-readable representations of machine language instructions.

- Each mnemonic opcode represents a specific machine instruction.

- Assembly language is a low-level programming language.

- It provides a one-to-one correspondence between instructions and mnemonic codes.

- Assembly language is specific to a particular computer architecture.

- It is often used for tasks that require direct hardware manipulation or performance optimization.

By using mnemonic opcodes, assembly language allows programmers to write code that is easier to understand and maintain compared to machine language. However, it still requires a deep understanding of the underlying computer architecture and instruction set.

In contrast, high-level languages like C, Java, or Python provide a higher level of abstraction, allowing programmers to write code that is more portable and easier to understand. These languages use more human-readable syntax and provide built-in functions and libraries for common tasks.

Overall, assembly language is a powerful tool for low-level programming and is commonly used in areas such as embedded systems, device drivers, and operating systems development.

Assembly language is a low-level programming language that uses mnemonic opcode instructions. It is a human-readable representation of machine language instructions. In assembly language, each mnemonic opcode represents a specific machine instruction that can be directly executed by the computer's hardware.

Explanation:

Assembly language is a programming language that provides a one-to-one correspondence between the instructions executed by a computer's central processing unit (CPU) and the mnemonic codes used to represent those instructions. It is considered a low-level language because it closely resembles the binary machine language of the computer.

Assembly language is specific to a particular computer architecture and is often used for tasks that require direct hardware manipulation or for optimizing performance. It provides a level of abstraction above machine language, making it easier for programmers to read and write code.

Key Points:

- Assembly language uses mnemonic opcode instructions.

- Mnemonic opcodes are human-readable representations of machine language instructions.

- Each mnemonic opcode represents a specific machine instruction.

- Assembly language is a low-level programming language.

- It provides a one-to-one correspondence between instructions and mnemonic codes.

- Assembly language is specific to a particular computer architecture.

- It is often used for tasks that require direct hardware manipulation or performance optimization.

By using mnemonic opcodes, assembly language allows programmers to write code that is easier to understand and maintain compared to machine language. However, it still requires a deep understanding of the underlying computer architecture and instruction set.

In contrast, high-level languages like C, Java, or Python provide a higher level of abstraction, allowing programmers to write code that is more portable and easier to understand. These languages use more human-readable syntax and provide built-in functions and libraries for common tasks.

Overall, assembly language is a powerful tool for low-level programming and is commonly used in areas such as embedded systems, device drivers, and operating systems development.

Chapter doubts & questions for Machine Instructions & Addressing Modes - Digital Circuits 2025 is part of Electronics and Communication Engineering (ECE) exam preparation. The chapters have been prepared according to the Electronics and Communication Engineering (ECE) exam syllabus. The Chapter doubts & questions, notes, tests & MCQs are made for Electronics and Communication Engineering (ECE) 2025 Exam. Find important definitions, questions, notes, meanings, examples, exercises, MCQs and online tests here.

Chapter doubts & questions of Machine Instructions & Addressing Modes - Digital Circuits in English & Hindi are available as part of Electronics and Communication Engineering (ECE) exam.

Download more important topics, notes, lectures and mock test series for Electronics and Communication Engineering (ECE) Exam by signing up for free.

Digital Circuits

76 videos|175 docs|70 tests

|

Contact Support

Our team is online on weekdays between 10 AM - 7 PM

Typical reply within 3 hours

|

Free Exam Preparation

at your Fingertips!

Access Free Study Material - Test Series, Structured Courses, Free Videos & Study Notes and Prepare for Your Exam With Ease

Join the 10M+ students on EduRev

Join the 10M+ students on EduRev

|

|

Create your account for free

OR

Forgot Password

OR

Signup to see your scores

go up within 7 days!

Access 1000+ FREE Docs, Videos and Tests

Takes less than 10 seconds to signup