Counters - Free MCQ Practice Test with solutions, UPSC Electrical Engineering

MCQ Practice Test & Solutions: Test: Counters (10 Questions)

You can prepare effectively for UPSC Electrical Engineering Optional Notes for UPSC with this dedicated MCQ Practice Test (available with solutions) on the important topic of "Test: Counters". These 10 questions have been designed by the experts with the latest curriculum of UPSC 2026, to help you master the concept.

Test Highlights:

- - Format: Multiple Choice Questions (MCQ)

- - Duration: 10 minutes

- - Number of Questions: 10

Sign up on EduRev for free to attempt this test and track your preparation progress.

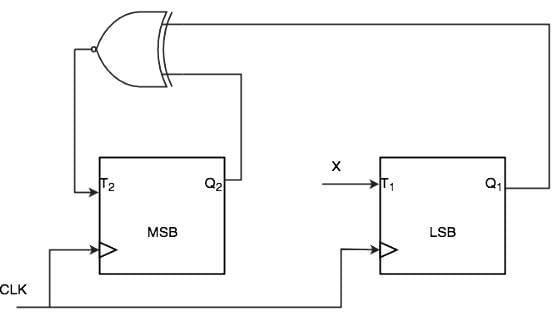

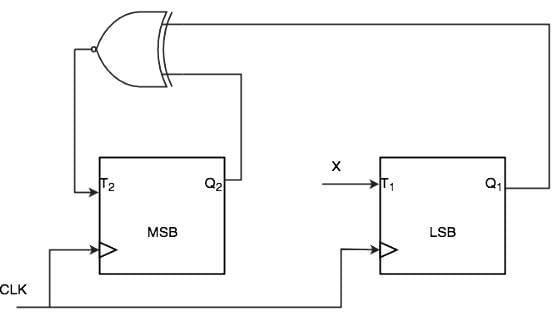

Consider the partial implementation of a 2-bit counter using T flip-flops following the sequence 0-2-3-1-0, as shown below

To complete the circuit, the input X should be

Detailed Solution: Question 1

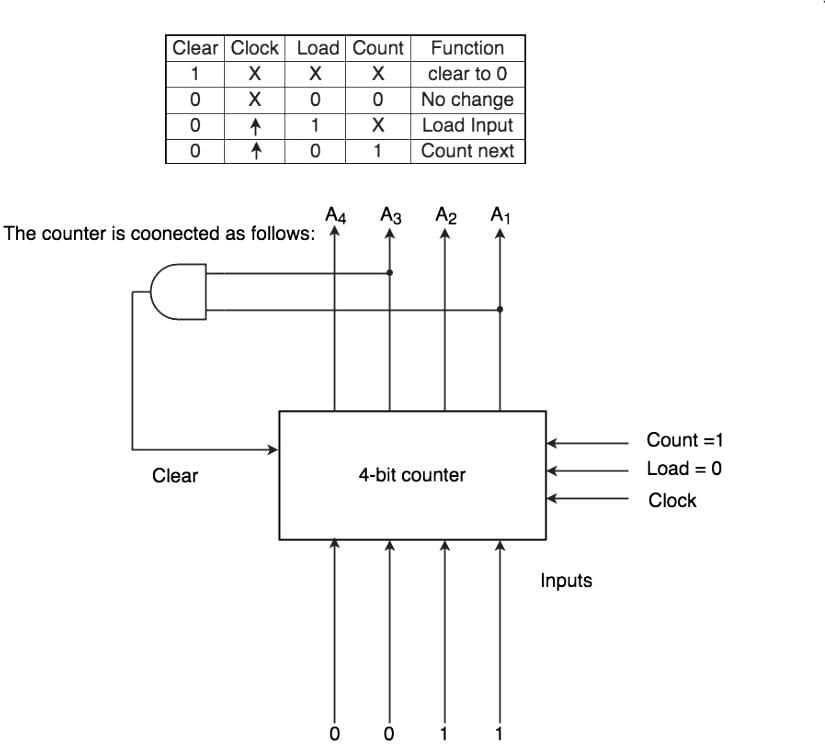

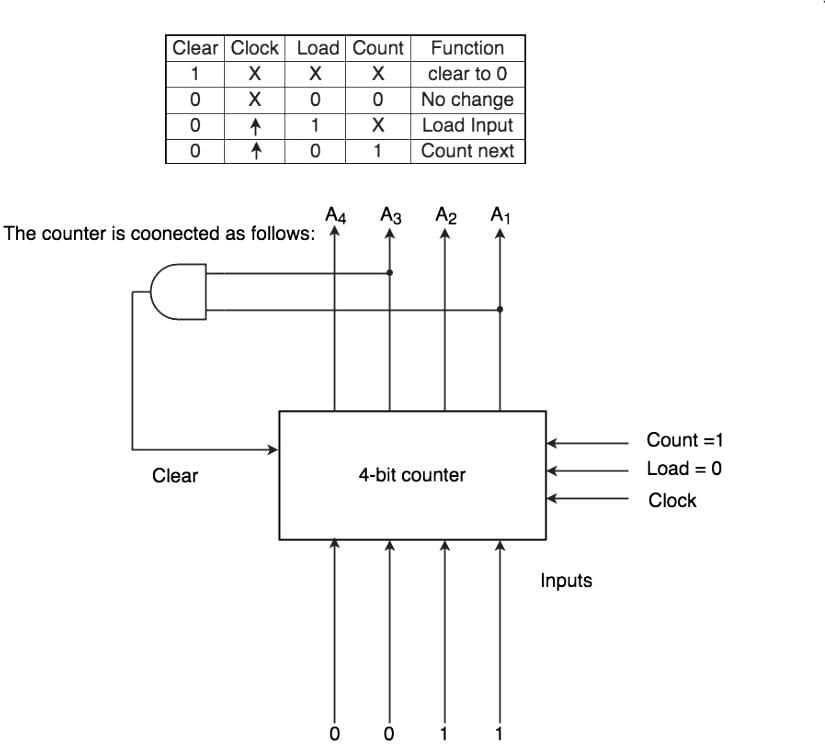

The control signal functions of a 4-bit binary counter are given below (where X is “don’t care”) The counter is connected as follows:

Assume that the counter and gate delays are negligible. If the counter starts at 0, then it cycles through the following sequence:

Detailed Solution: Question 2

Detailed Solution: Question 3

Detailed Solution: Question 4

What is the maximum possible range of bit-count specifically in n-bit binary counter consisting of ‘n’ number of flip-flops?

Detailed Solution: Question 5

Detailed Solution: Question 6

Detailed Solution: Question 7

Detailed Solution: Question 8

Detailed Solution: Question 9

The parallel outputs of a counter circuit represent the _____________

Detailed Solution: Question 10

550 videos|590 docs|343 tests |

550 videos|590 docs|343 tests |