Electrical Engineering (EE) Exam > Electrical Engineering (EE) Questions > A full adder circuit can be implemented using...

Start Learning for Free

A full adder circuit can be implemented using:

1. One 3 x 8 decoder and two OR gates.

2. One 3 x 8 decoder, one OR gate and a NOT gate.

3. Two half adders and one OR gate.

4. Two half adders and one NOT gate.

5. Nine NAND/NOR gates.

6. 6 NAND/NOR gates.

Select the correct code from the given options.

1. One 3 x 8 decoder and two OR gates.

2. One 3 x 8 decoder, one OR gate and a NOT gate.

3. Two half adders and one OR gate.

4. Two half adders and one NOT gate.

5. Nine NAND/NOR gates.

6. 6 NAND/NOR gates.

Select the correct code from the given options.

- a)2, 4 and 5

- b)1, 4 and 6

- c)1, 3 and 5

- d)2, 3 and 6

Correct answer is option 'C'. Can you explain this answer?

Verified Answer

A full adder circuit can be implemented using:1. One 3 x 8 decoder and...

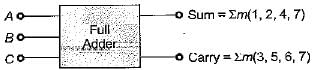

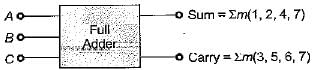

A full adder is used to add three input bits (A, R and C) to give two outputs namely sum and carry as shown below:

For its implementation we require either of the following:

For its implementation we require either of the following:

- One 3 x 8 decoder and two OR gates.

- Two half adders and one OR gate.

- Nine NAND/NOR gates.

Most Upvoted Answer

A full adder circuit can be implemented using:1. One 3 x 8 decoder and...

Understanding Full Adder Implementation

A full adder is a digital circuit that computes the sum of three binary bits: two significant bits and a carry-in bit. The full adder outputs a sum bit and a carry-out bit. Let's analyze the given options for implementing a full adder.

1. Using a 3 x 8 Decoder and Two OR Gates

- A 3 x 8 decoder can decode three input bits into 8 output lines.

- You can use the outputs to represent various combinations of inputs and use OR gates to combine specific outputs to generate sum and carry.

2. Using a 3 x 8 Decoder, One OR Gate, and a NOT Gate

- This combination is also valid. The NOT gate can help in manipulating the inputs or outputs to achieve the desired logic for sum and carry.

3. Using Two Half Adders and One OR Gate

- This method is a classic implementation. A half adder can handle two inputs, and combining two half adders with an OR gate effectively produces the correct sum and carry for three inputs.

4. Using Two Half Adders and One NOT Gate

- This configuration is less common as it may not yield the correct output for all possible input combinations.

5. Using Nine NAND/NOR Gates

- This is a valid implementation. Full adders can be constructed using various combinations of NAND/NOR gates, but nine gates may be excessive.

6. Using Six NAND/NOR Gates

- This option is also possible. Full adders can efficiently be created with fewer gates as well.

Conclusion

The valid implementations of a full adder from the options provided are:

- Option 1 (3 x 8 Decoder and two OR gates)

- Option 3 (Two half adders and one OR gate)

- Option 5 (Nine NAND/NOR gates)

Thus, the correct answer is option C: 1, 3, and 5.

A full adder is a digital circuit that computes the sum of three binary bits: two significant bits and a carry-in bit. The full adder outputs a sum bit and a carry-out bit. Let's analyze the given options for implementing a full adder.

1. Using a 3 x 8 Decoder and Two OR Gates

- A 3 x 8 decoder can decode three input bits into 8 output lines.

- You can use the outputs to represent various combinations of inputs and use OR gates to combine specific outputs to generate sum and carry.

2. Using a 3 x 8 Decoder, One OR Gate, and a NOT Gate

- This combination is also valid. The NOT gate can help in manipulating the inputs or outputs to achieve the desired logic for sum and carry.

3. Using Two Half Adders and One OR Gate

- This method is a classic implementation. A half adder can handle two inputs, and combining two half adders with an OR gate effectively produces the correct sum and carry for three inputs.

4. Using Two Half Adders and One NOT Gate

- This configuration is less common as it may not yield the correct output for all possible input combinations.

5. Using Nine NAND/NOR Gates

- This is a valid implementation. Full adders can be constructed using various combinations of NAND/NOR gates, but nine gates may be excessive.

6. Using Six NAND/NOR Gates

- This option is also possible. Full adders can efficiently be created with fewer gates as well.

Conclusion

The valid implementations of a full adder from the options provided are:

- Option 1 (3 x 8 Decoder and two OR gates)

- Option 3 (Two half adders and one OR gate)

- Option 5 (Nine NAND/NOR gates)

Thus, the correct answer is option C: 1, 3, and 5.

|

Explore Courses for Electrical Engineering (EE) exam

|

|

Similar Electrical Engineering (EE) Doubts

Question Description

A full adder circuit can be implemented using:1. One 3 x 8 decoder and two OR gates.2. One 3 x 8 decoder, one OR gate and a NOT gate.3. Two half adders and one OR gate.4. Two half adders and one NOT gate.5. Nine NAND/NOR gates.6. 6 NAND/NOR gates.Select the correct code from the given options.a)2, 4 and 5b)1, 4 and 6c)1, 3 and 5d)2, 3 and 6Correct answer is option 'C'. Can you explain this answer? for Electrical Engineering (EE) 2025 is part of Electrical Engineering (EE) preparation. The Question and answers have been prepared according to the Electrical Engineering (EE) exam syllabus. Information about A full adder circuit can be implemented using:1. One 3 x 8 decoder and two OR gates.2. One 3 x 8 decoder, one OR gate and a NOT gate.3. Two half adders and one OR gate.4. Two half adders and one NOT gate.5. Nine NAND/NOR gates.6. 6 NAND/NOR gates.Select the correct code from the given options.a)2, 4 and 5b)1, 4 and 6c)1, 3 and 5d)2, 3 and 6Correct answer is option 'C'. Can you explain this answer? covers all topics & solutions for Electrical Engineering (EE) 2025 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for A full adder circuit can be implemented using:1. One 3 x 8 decoder and two OR gates.2. One 3 x 8 decoder, one OR gate and a NOT gate.3. Two half adders and one OR gate.4. Two half adders and one NOT gate.5. Nine NAND/NOR gates.6. 6 NAND/NOR gates.Select the correct code from the given options.a)2, 4 and 5b)1, 4 and 6c)1, 3 and 5d)2, 3 and 6Correct answer is option 'C'. Can you explain this answer?.

A full adder circuit can be implemented using:1. One 3 x 8 decoder and two OR gates.2. One 3 x 8 decoder, one OR gate and a NOT gate.3. Two half adders and one OR gate.4. Two half adders and one NOT gate.5. Nine NAND/NOR gates.6. 6 NAND/NOR gates.Select the correct code from the given options.a)2, 4 and 5b)1, 4 and 6c)1, 3 and 5d)2, 3 and 6Correct answer is option 'C'. Can you explain this answer? for Electrical Engineering (EE) 2025 is part of Electrical Engineering (EE) preparation. The Question and answers have been prepared according to the Electrical Engineering (EE) exam syllabus. Information about A full adder circuit can be implemented using:1. One 3 x 8 decoder and two OR gates.2. One 3 x 8 decoder, one OR gate and a NOT gate.3. Two half adders and one OR gate.4. Two half adders and one NOT gate.5. Nine NAND/NOR gates.6. 6 NAND/NOR gates.Select the correct code from the given options.a)2, 4 and 5b)1, 4 and 6c)1, 3 and 5d)2, 3 and 6Correct answer is option 'C'. Can you explain this answer? covers all topics & solutions for Electrical Engineering (EE) 2025 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for A full adder circuit can be implemented using:1. One 3 x 8 decoder and two OR gates.2. One 3 x 8 decoder, one OR gate and a NOT gate.3. Two half adders and one OR gate.4. Two half adders and one NOT gate.5. Nine NAND/NOR gates.6. 6 NAND/NOR gates.Select the correct code from the given options.a)2, 4 and 5b)1, 4 and 6c)1, 3 and 5d)2, 3 and 6Correct answer is option 'C'. Can you explain this answer?.

Solutions for A full adder circuit can be implemented using:1. One 3 x 8 decoder and two OR gates.2. One 3 x 8 decoder, one OR gate and a NOT gate.3. Two half adders and one OR gate.4. Two half adders and one NOT gate.5. Nine NAND/NOR gates.6. 6 NAND/NOR gates.Select the correct code from the given options.a)2, 4 and 5b)1, 4 and 6c)1, 3 and 5d)2, 3 and 6Correct answer is option 'C'. Can you explain this answer? in English & in Hindi are available as part of our courses for Electrical Engineering (EE).

Download more important topics, notes, lectures and mock test series for Electrical Engineering (EE) Exam by signing up for free.

Here you can find the meaning of A full adder circuit can be implemented using:1. One 3 x 8 decoder and two OR gates.2. One 3 x 8 decoder, one OR gate and a NOT gate.3. Two half adders and one OR gate.4. Two half adders and one NOT gate.5. Nine NAND/NOR gates.6. 6 NAND/NOR gates.Select the correct code from the given options.a)2, 4 and 5b)1, 4 and 6c)1, 3 and 5d)2, 3 and 6Correct answer is option 'C'. Can you explain this answer? defined & explained in the simplest way possible. Besides giving the explanation of

A full adder circuit can be implemented using:1. One 3 x 8 decoder and two OR gates.2. One 3 x 8 decoder, one OR gate and a NOT gate.3. Two half adders and one OR gate.4. Two half adders and one NOT gate.5. Nine NAND/NOR gates.6. 6 NAND/NOR gates.Select the correct code from the given options.a)2, 4 and 5b)1, 4 and 6c)1, 3 and 5d)2, 3 and 6Correct answer is option 'C'. Can you explain this answer?, a detailed solution for A full adder circuit can be implemented using:1. One 3 x 8 decoder and two OR gates.2. One 3 x 8 decoder, one OR gate and a NOT gate.3. Two half adders and one OR gate.4. Two half adders and one NOT gate.5. Nine NAND/NOR gates.6. 6 NAND/NOR gates.Select the correct code from the given options.a)2, 4 and 5b)1, 4 and 6c)1, 3 and 5d)2, 3 and 6Correct answer is option 'C'. Can you explain this answer? has been provided alongside types of A full adder circuit can be implemented using:1. One 3 x 8 decoder and two OR gates.2. One 3 x 8 decoder, one OR gate and a NOT gate.3. Two half adders and one OR gate.4. Two half adders and one NOT gate.5. Nine NAND/NOR gates.6. 6 NAND/NOR gates.Select the correct code from the given options.a)2, 4 and 5b)1, 4 and 6c)1, 3 and 5d)2, 3 and 6Correct answer is option 'C'. Can you explain this answer? theory, EduRev gives you an

ample number of questions to practice A full adder circuit can be implemented using:1. One 3 x 8 decoder and two OR gates.2. One 3 x 8 decoder, one OR gate and a NOT gate.3. Two half adders and one OR gate.4. Two half adders and one NOT gate.5. Nine NAND/NOR gates.6. 6 NAND/NOR gates.Select the correct code from the given options.a)2, 4 and 5b)1, 4 and 6c)1, 3 and 5d)2, 3 and 6Correct answer is option 'C'. Can you explain this answer? tests, examples and also practice Electrical Engineering (EE) tests.

|

Explore Courses for Electrical Engineering (EE) exam

|

|

Signup to solve all Doubts

Signup to see your scores go up within 7 days! Learn & Practice with 1000+ FREE Notes, Videos & Tests.