Electrical Engineering (EE) Exam > Electrical Engineering (EE) Questions > Which logic family dissipates the minimum pow...

Start Learning for Free

Which logic family dissipates the minimum power?

- a)DTL

- b)TTL

- c)ECL

- d)CMOS

Correct answer is option 'D'. Can you explain this answer?

Verified Answer

Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSC...

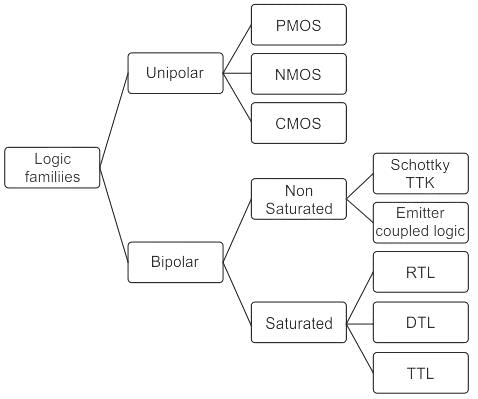

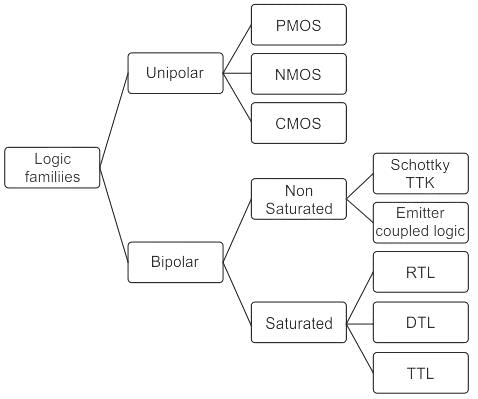

A logic family is one of two related concepts: A logic family of monolithic digital integrated circuit devices is a group of electronic logic gates constructed using one of several different designs, usually with compatible logic levels and power supply characteristics within a family.

Most Upvoted Answer

Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSC...

< b="" />CMOS (Complementary Metal-Oxide-Semiconductor)< />

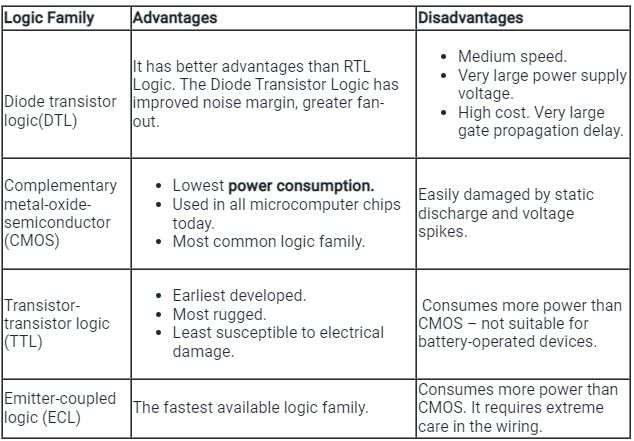

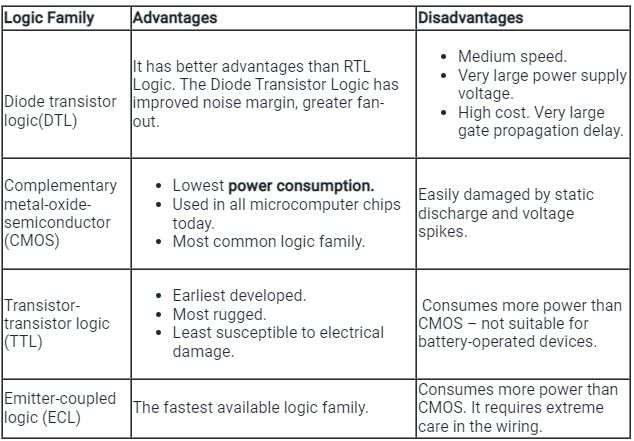

CMOS, or Complementary Metal-Oxide-Semiconductor, is a type of logic family that dissipates the minimum power compared to other logic families such as DTL (Diode-Transistor Logic), TTL (Transistor-Transistor Logic), and ECL (Emitter-Coupled Logic). There are several reasons why CMOS is considered to be the most power-efficient logic family:

< b="" />1. Low Static Power Dissipation:< />

CMOS operates on the principle of using complementary pairs of MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors), one P-channel and one N-channel, to form logic gates. When there is no switching activity, CMOS gates consume very little static power. This is because the MOSFETs in the CMOS gates are designed in such a way that they have a very high input impedance and do not draw any significant current when in a static state.

< b="" />2. Low Dynamic Power Dissipation:< />

Dynamic power dissipation occurs when the CMOS gates switch states. During this switching activity, there is a brief period of time when both the P-channel and N-channel transistors are conducting, leading to a brief short-circuit current path from the power supply to the ground. However, this short-circuit current is limited by the resistance of the MOSFETs, which is typically very high. As a result, the dynamic power dissipation in CMOS is significantly lower compared to other logic families.

< b="" />3. Symmetrical Rise and Fall Times:< />

CMOS gates have symmetrical rise and fall times, which means that the time required to transition from a logic low to a logic high state is the same as the time required to transition from a logic high to a logic low state. This symmetry allows for efficient power utilization and reduces the overall power dissipation in CMOS circuits.

< b="" />4. High Noise Margin:< />

CMOS gates have a high noise margin, which means they are less susceptible to noise and interference. This allows for better noise immunity and reduces the likelihood of erroneous switching, further contributing to the power efficiency of CMOS circuits.

In conclusion, CMOS logic family dissipates the minimum power compared to other logic families due to its low static and dynamic power dissipation, symmetrical rise and fall times, and high noise margin. These characteristics make CMOS an ideal choice for low-power applications, such as portable devices, where power consumption is a critical factor.

CMOS, or Complementary Metal-Oxide-Semiconductor, is a type of logic family that dissipates the minimum power compared to other logic families such as DTL (Diode-Transistor Logic), TTL (Transistor-Transistor Logic), and ECL (Emitter-Coupled Logic). There are several reasons why CMOS is considered to be the most power-efficient logic family:

< b="" />1. Low Static Power Dissipation:< />

CMOS operates on the principle of using complementary pairs of MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors), one P-channel and one N-channel, to form logic gates. When there is no switching activity, CMOS gates consume very little static power. This is because the MOSFETs in the CMOS gates are designed in such a way that they have a very high input impedance and do not draw any significant current when in a static state.

< b="" />2. Low Dynamic Power Dissipation:< />

Dynamic power dissipation occurs when the CMOS gates switch states. During this switching activity, there is a brief period of time when both the P-channel and N-channel transistors are conducting, leading to a brief short-circuit current path from the power supply to the ground. However, this short-circuit current is limited by the resistance of the MOSFETs, which is typically very high. As a result, the dynamic power dissipation in CMOS is significantly lower compared to other logic families.

< b="" />3. Symmetrical Rise and Fall Times:< />

CMOS gates have symmetrical rise and fall times, which means that the time required to transition from a logic low to a logic high state is the same as the time required to transition from a logic high to a logic low state. This symmetry allows for efficient power utilization and reduces the overall power dissipation in CMOS circuits.

< b="" />4. High Noise Margin:< />

CMOS gates have a high noise margin, which means they are less susceptible to noise and interference. This allows for better noise immunity and reduces the likelihood of erroneous switching, further contributing to the power efficiency of CMOS circuits.

In conclusion, CMOS logic family dissipates the minimum power compared to other logic families due to its low static and dynamic power dissipation, symmetrical rise and fall times, and high noise margin. These characteristics make CMOS an ideal choice for low-power applications, such as portable devices, where power consumption is a critical factor.

Free Test

FREE

| Start Free Test |

Community Answer

Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSC...

A logic family is one of two related concepts: A logic family of monolithic digital integrated circuit devices is a group of electronic logic gates constructed using one of several different designs, usually with compatible logic levels and power supply characteristics within a family.

|

Explore Courses for Electrical Engineering (EE) exam

|

|

Question Description

Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSCorrect answer is option 'D'. Can you explain this answer? for Electrical Engineering (EE) 2025 is part of Electrical Engineering (EE) preparation. The Question and answers have been prepared according to the Electrical Engineering (EE) exam syllabus. Information about Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSCorrect answer is option 'D'. Can you explain this answer? covers all topics & solutions for Electrical Engineering (EE) 2025 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSCorrect answer is option 'D'. Can you explain this answer?.

Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSCorrect answer is option 'D'. Can you explain this answer? for Electrical Engineering (EE) 2025 is part of Electrical Engineering (EE) preparation. The Question and answers have been prepared according to the Electrical Engineering (EE) exam syllabus. Information about Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSCorrect answer is option 'D'. Can you explain this answer? covers all topics & solutions for Electrical Engineering (EE) 2025 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSCorrect answer is option 'D'. Can you explain this answer?.

Solutions for Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSCorrect answer is option 'D'. Can you explain this answer? in English & in Hindi are available as part of our courses for Electrical Engineering (EE).

Download more important topics, notes, lectures and mock test series for Electrical Engineering (EE) Exam by signing up for free.

Here you can find the meaning of Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSCorrect answer is option 'D'. Can you explain this answer? defined & explained in the simplest way possible. Besides giving the explanation of

Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSCorrect answer is option 'D'. Can you explain this answer?, a detailed solution for Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSCorrect answer is option 'D'. Can you explain this answer? has been provided alongside types of Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSCorrect answer is option 'D'. Can you explain this answer? theory, EduRev gives you an

ample number of questions to practice Which logic family dissipates the minimum power?a)DTLb)TTLc)ECLd)CMOSCorrect answer is option 'D'. Can you explain this answer? tests, examples and also practice Electrical Engineering (EE) tests.

|

Explore Courses for Electrical Engineering (EE) exam

|

|

Signup for Free!

Signup to see your scores go up within 7 days! Learn & Practice with 1000+ FREE Notes, Videos & Tests.