Electrical Engineering (EE) Exam > Electrical Engineering (EE) Questions > The maximum clock frequency in MHz of a 4-sta...

Start Learning for Free

The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)

Correct answer is between '12.3,12.7'. Can you explain this answer?

Most Upvoted Answer

The maximum clock frequency in MHz of a 4-stage ripple counter, utiliz...

Given:

- The ripple counter has 4 stages.

- Each flip-flop in the counter has a propagation delay of 20 ns.

To find:

- The maximum clock frequency in MHz.

Explanation:

A ripple counter is a type of digital circuit that counts in binary sequence. In a 4-stage ripple counter, there are four flip-flops connected in series, such that the output of each flip-flop serves as the clock input for the next flip-flop. The output of the last flip-flop is the most significant bit (MSB) of the counter.

The maximum clock frequency in a ripple counter is limited by the propagation delay of the flip-flops. The propagation delay is the time taken for the output of a flip-flop to respond to a change in the input. In this case, each flip-flop has a propagation delay of 20 ns.

Calculating the maximum clock frequency:

The maximum clock frequency can be calculated using the formula:

Maximum clock frequency = 1 / (2 * propagation delay)

In this case, the propagation delay is 20 ns, so:

Maximum clock frequency = 1 / (2 * 20 ns) = 1 / (40 ns) = 25 MHz

However, it's important to note that the ripple counter has four stages, and each stage introduces an additional propagation delay. Since the outputs of the flip-flops are connected in series, the total propagation delay of the counter is the sum of the individual propagation delays.

In this case, the total propagation delay is 4 * 20 ns = 80 ns.

Adjusting for the total propagation delay:

To calculate the maximum clock frequency, we need to adjust for the total propagation delay of the counter. The adjusted formula becomes:

Maximum clock frequency = 1 / (2 * total propagation delay)

Maximum clock frequency = 1 / (2 * 80 ns) = 1 / (160 ns) = 6.25 MHz

Therefore, the maximum clock frequency of the 4-stage ripple counter, utilizing flip-flops with a propagation delay of 20 ns, is approximately 6.25 MHz.

Round off:

Rounding off the answer to one decimal place, the maximum clock frequency is between 6.2 MHz and 6.3 MHz.

- The ripple counter has 4 stages.

- Each flip-flop in the counter has a propagation delay of 20 ns.

To find:

- The maximum clock frequency in MHz.

Explanation:

A ripple counter is a type of digital circuit that counts in binary sequence. In a 4-stage ripple counter, there are four flip-flops connected in series, such that the output of each flip-flop serves as the clock input for the next flip-flop. The output of the last flip-flop is the most significant bit (MSB) of the counter.

The maximum clock frequency in a ripple counter is limited by the propagation delay of the flip-flops. The propagation delay is the time taken for the output of a flip-flop to respond to a change in the input. In this case, each flip-flop has a propagation delay of 20 ns.

Calculating the maximum clock frequency:

The maximum clock frequency can be calculated using the formula:

Maximum clock frequency = 1 / (2 * propagation delay)

In this case, the propagation delay is 20 ns, so:

Maximum clock frequency = 1 / (2 * 20 ns) = 1 / (40 ns) = 25 MHz

However, it's important to note that the ripple counter has four stages, and each stage introduces an additional propagation delay. Since the outputs of the flip-flops are connected in series, the total propagation delay of the counter is the sum of the individual propagation delays.

In this case, the total propagation delay is 4 * 20 ns = 80 ns.

Adjusting for the total propagation delay:

To calculate the maximum clock frequency, we need to adjust for the total propagation delay of the counter. The adjusted formula becomes:

Maximum clock frequency = 1 / (2 * total propagation delay)

Maximum clock frequency = 1 / (2 * 80 ns) = 1 / (160 ns) = 6.25 MHz

Therefore, the maximum clock frequency of the 4-stage ripple counter, utilizing flip-flops with a propagation delay of 20 ns, is approximately 6.25 MHz.

Round off:

Rounding off the answer to one decimal place, the maximum clock frequency is between 6.2 MHz and 6.3 MHz.

Free Test

FREE

| Start Free Test |

Community Answer

The maximum clock frequency in MHz of a 4-stage ripple counter, utiliz...

Concept:

For the n-stage ripple counter, the no. of flip-flops used are n.

If Each flip flop is having propagation delay of tp seconds.

Then overall propagation delay of the n-stage ripple counter is 'ntp'

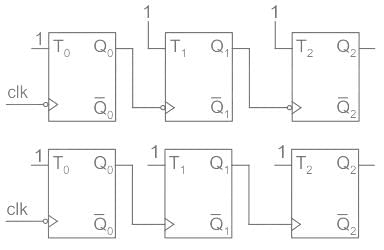

Both of the above diagrams is a 3 stage up counter.

i.e., 3 flip-flops are used.

In order to obtain Q2, the 3 clocks will be used at a different instant or at the instant when each flip flop will get their input.

If each flip flop is having 'tp' as propagation delay, then to get output, the overall propagation Delay will be sum of the propagation Delay of each flip flop.

Explanation:

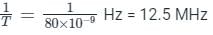

Given

Ripple counter 4 flip flop

tp = 20 n second for each flip flop.

T = n tp = total propagation delay

⇒ T = 4 × 20 n sec = 80 n sec

Clock frequency =

|

Explore Courses for Electrical Engineering (EE) exam

|

|

Question Description

The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)Correct answer is between '12.3,12.7'. Can you explain this answer? for Electrical Engineering (EE) 2025 is part of Electrical Engineering (EE) preparation. The Question and answers have been prepared according to the Electrical Engineering (EE) exam syllabus. Information about The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)Correct answer is between '12.3,12.7'. Can you explain this answer? covers all topics & solutions for Electrical Engineering (EE) 2025 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)Correct answer is between '12.3,12.7'. Can you explain this answer?.

The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)Correct answer is between '12.3,12.7'. Can you explain this answer? for Electrical Engineering (EE) 2025 is part of Electrical Engineering (EE) preparation. The Question and answers have been prepared according to the Electrical Engineering (EE) exam syllabus. Information about The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)Correct answer is between '12.3,12.7'. Can you explain this answer? covers all topics & solutions for Electrical Engineering (EE) 2025 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)Correct answer is between '12.3,12.7'. Can you explain this answer?.

Solutions for The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)Correct answer is between '12.3,12.7'. Can you explain this answer? in English & in Hindi are available as part of our courses for Electrical Engineering (EE).

Download more important topics, notes, lectures and mock test series for Electrical Engineering (EE) Exam by signing up for free.

Here you can find the meaning of The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)Correct answer is between '12.3,12.7'. Can you explain this answer? defined & explained in the simplest way possible. Besides giving the explanation of

The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)Correct answer is between '12.3,12.7'. Can you explain this answer?, a detailed solution for The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)Correct answer is between '12.3,12.7'. Can you explain this answer? has been provided alongside types of The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)Correct answer is between '12.3,12.7'. Can you explain this answer? theory, EduRev gives you an

ample number of questions to practice The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)Correct answer is between '12.3,12.7'. Can you explain this answer? tests, examples and also practice Electrical Engineering (EE) tests.

|

Explore Courses for Electrical Engineering (EE) exam

|

|

Signup to solve all Doubts

Signup to see your scores go up within 7 days! Learn & Practice with 1000+ FREE Notes, Videos & Tests.