Computer Science Engineering (CSE) Exam > Computer Science Engineering (CSE) Questions > Consider a 4-way set associative cache (initi...

Start Learning for Free

Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:

0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.

0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.

Which one of the following memory block will NOT be in cache if LRU replacement policy is used?

- a)159, 1

- b)216, 1

- c)159, 73

- d)216, 73

Correct answer is option 'B'. Can you explain this answer?

| FREE This question is part of | Download PDF Attempt this Test |

Most Upvoted Answer

Consider a 4-way set associative cache (initially empty) with total 16...

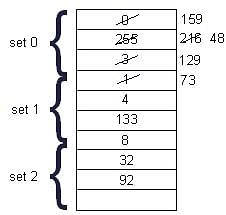

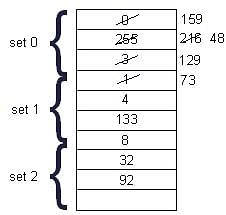

Total 3 sets are there in the cache and each set contains 3 blocks. The LRU replacement is shown here. Access to block 48 replaces block 216, not block 159 because of LRU strategy. Acccess to block 73 replaces block 1.

Free Test

FREE

| Start Free Test |

Community Answer

Consider a 4-way set associative cache (initially empty) with total 16...

Given Information:

- 4-way set associative cache with 16 cache blocks (4 sets with 4 blocks each)

- Main memory consists of 256 blocks

- Request for memory blocks: 0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155

- LRU replacement policy is used

Explanation:

Step 1: Set up the cache

- Divide the cache into 4 sets, each with 4 blocks.

- Initially, the cache is empty.

Step 2: Processing the memory requests

- Process each memory request one by one and check if the requested block is present in the cache.

Request 0:

- The cache is empty, so block 0 is not present in the cache.

- Add block 0 to the cache.

Request 255:

- The cache is still empty, so block 255 is not present in the cache.

- Add block 255 to the cache.

Request 1:

- The cache now contains blocks 0 and 255.

- Check if block 1 is present in the cache.

- Block 1 is not present in the cache.

- Replace the least recently used block, which is block 0, with block 1.

Request 4:

- The cache now contains blocks 1 and 255.

- Check if block 4 is present in the cache.

- Block 4 is not present in the cache.

- Replace the least recently used block, which is block 255, with block 4.

Request 3:

- The cache now contains blocks 1 and 4.

- Check if block 3 is present in the cache.

- Block 3 is not present in the cache.

- Replace the least recently used block, which is block 1, with block 3.

Request 8:

- The cache now contains blocks 3 and 4.

- Check if block 8 is present in the cache.

- Block 8 is not present in the cache.

- Replace the least recently used block, which is block 4, with block 8.

Request 133:

- The cache now contains blocks 3 and 8.

- Check if block 133 is present in the cache.

- Block 133 is not present in the cache.

- Replace the least recently used block, which is block 3, with block 133.

Request 159:

- The cache now contains blocks 8 and 133.

- Check if block 159 is present in the cache.

- Block 159 is not present in the cache.

- Replace the least recently used block, which is block 8, with block 159.

Request 216:

- The cache now contains blocks 133 and 159.

- Check if block 216 is present in the cache.

- Block 216 is not present in the cache.

- Replace the least recently used block, which is block 133, with block 216.

Request 129:

- The cache now contains blocks 159 and 216.

- 4-way set associative cache with 16 cache blocks (4 sets with 4 blocks each)

- Main memory consists of 256 blocks

- Request for memory blocks: 0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155

- LRU replacement policy is used

Explanation:

Step 1: Set up the cache

- Divide the cache into 4 sets, each with 4 blocks.

- Initially, the cache is empty.

Step 2: Processing the memory requests

- Process each memory request one by one and check if the requested block is present in the cache.

Request 0:

- The cache is empty, so block 0 is not present in the cache.

- Add block 0 to the cache.

Request 255:

- The cache is still empty, so block 255 is not present in the cache.

- Add block 255 to the cache.

Request 1:

- The cache now contains blocks 0 and 255.

- Check if block 1 is present in the cache.

- Block 1 is not present in the cache.

- Replace the least recently used block, which is block 0, with block 1.

Request 4:

- The cache now contains blocks 1 and 255.

- Check if block 4 is present in the cache.

- Block 4 is not present in the cache.

- Replace the least recently used block, which is block 255, with block 4.

Request 3:

- The cache now contains blocks 1 and 4.

- Check if block 3 is present in the cache.

- Block 3 is not present in the cache.

- Replace the least recently used block, which is block 1, with block 3.

Request 8:

- The cache now contains blocks 3 and 4.

- Check if block 8 is present in the cache.

- Block 8 is not present in the cache.

- Replace the least recently used block, which is block 4, with block 8.

Request 133:

- The cache now contains blocks 3 and 8.

- Check if block 133 is present in the cache.

- Block 133 is not present in the cache.

- Replace the least recently used block, which is block 3, with block 133.

Request 159:

- The cache now contains blocks 8 and 133.

- Check if block 159 is present in the cache.

- Block 159 is not present in the cache.

- Replace the least recently used block, which is block 8, with block 159.

Request 216:

- The cache now contains blocks 133 and 159.

- Check if block 216 is present in the cache.

- Block 216 is not present in the cache.

- Replace the least recently used block, which is block 133, with block 216.

Request 129:

- The cache now contains blocks 159 and 216.

Attention Computer Science Engineering (CSE) Students!

To make sure you are not studying endlessly, EduRev has designed Computer Science Engineering (CSE) study material, with Structured Courses, Videos, & Test Series. Plus get personalized analysis, doubt solving and improvement plans to achieve a great score in Computer Science Engineering (CSE).

|

Explore Courses for Computer Science Engineering (CSE) exam

|

|

Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.Which one of the following memory block will NOT be in cache if LRU replacement policy is used?a)159, 1b)216, 1c)159, 73d)216, 73Correct answer is option 'B'. Can you explain this answer?

Question Description

Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.Which one of the following memory block will NOT be in cache if LRU replacement policy is used?a)159, 1b)216, 1c)159, 73d)216, 73Correct answer is option 'B'. Can you explain this answer? for Computer Science Engineering (CSE) 2024 is part of Computer Science Engineering (CSE) preparation. The Question and answers have been prepared according to the Computer Science Engineering (CSE) exam syllabus. Information about Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.Which one of the following memory block will NOT be in cache if LRU replacement policy is used?a)159, 1b)216, 1c)159, 73d)216, 73Correct answer is option 'B'. Can you explain this answer? covers all topics & solutions for Computer Science Engineering (CSE) 2024 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.Which one of the following memory block will NOT be in cache if LRU replacement policy is used?a)159, 1b)216, 1c)159, 73d)216, 73Correct answer is option 'B'. Can you explain this answer?.

Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.Which one of the following memory block will NOT be in cache if LRU replacement policy is used?a)159, 1b)216, 1c)159, 73d)216, 73Correct answer is option 'B'. Can you explain this answer? for Computer Science Engineering (CSE) 2024 is part of Computer Science Engineering (CSE) preparation. The Question and answers have been prepared according to the Computer Science Engineering (CSE) exam syllabus. Information about Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.Which one of the following memory block will NOT be in cache if LRU replacement policy is used?a)159, 1b)216, 1c)159, 73d)216, 73Correct answer is option 'B'. Can you explain this answer? covers all topics & solutions for Computer Science Engineering (CSE) 2024 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.Which one of the following memory block will NOT be in cache if LRU replacement policy is used?a)159, 1b)216, 1c)159, 73d)216, 73Correct answer is option 'B'. Can you explain this answer?.

Solutions for Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.Which one of the following memory block will NOT be in cache if LRU replacement policy is used?a)159, 1b)216, 1c)159, 73d)216, 73Correct answer is option 'B'. Can you explain this answer? in English & in Hindi are available as part of our courses for Computer Science Engineering (CSE).

Download more important topics, notes, lectures and mock test series for Computer Science Engineering (CSE) Exam by signing up for free.

Here you can find the meaning of Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.Which one of the following memory block will NOT be in cache if LRU replacement policy is used?a)159, 1b)216, 1c)159, 73d)216, 73Correct answer is option 'B'. Can you explain this answer? defined & explained in the simplest way possible. Besides giving the explanation of

Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.Which one of the following memory block will NOT be in cache if LRU replacement policy is used?a)159, 1b)216, 1c)159, 73d)216, 73Correct answer is option 'B'. Can you explain this answer?, a detailed solution for Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.Which one of the following memory block will NOT be in cache if LRU replacement policy is used?a)159, 1b)216, 1c)159, 73d)216, 73Correct answer is option 'B'. Can you explain this answer? has been provided alongside types of Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.Which one of the following memory block will NOT be in cache if LRU replacement policy is used?a)159, 1b)216, 1c)159, 73d)216, 73Correct answer is option 'B'. Can you explain this answer? theory, EduRev gives you an

ample number of questions to practice Consider a 4-way set associative cache (initially empty) with total 16 cache blocks. The main memory consists of 256 blocks and the request for memory blocks is in the following order:0, 255, 1, 4, 3, 8, 133, 159, 216, 129, 63, 8, 48, 32, 73, 92, 155.Which one of the following memory block will NOT be in cache if LRU replacement policy is used?a)159, 1b)216, 1c)159, 73d)216, 73Correct answer is option 'B'. Can you explain this answer? tests, examples and also practice Computer Science Engineering (CSE) tests.

|

Explore Courses for Computer Science Engineering (CSE) exam

|

|

Suggested Free Tests

Signup for Free!

Signup to see your scores go up within 7 days! Learn & Practice with 1000+ FREE Notes, Videos & Tests.