All questions of Digital Logic for Computer Science Engineering (CSE) Exam

The

16 -bit

2` s complement representation of an integer is

1111 1111 1111 0101 ; its decimal representation is ______________.

Correct answer is '-11'. Can you explain this answer?

The

16 -bit

2` s complement representation of an integer is

1111 1111 1111 0101 ; its decimal representation is ______________.

16 -bit

2` s complement representation of an integer is

1111 1111 1111 0101 ; its decimal representation is ______________.

|

|

Shreya Sen answered |

for 2's complement 1 111 1111 1111 0101 →2′scomplement→2′scomplement 1 000 0000 0000 1011

1st bit is same not involved in 2's complement same with 1's complement. since msb bit for sign.

Take one's complement and add 1 we get 11, and as it is negative number we get answer as -11

1st bit is same not involved in 2's complement same with 1's complement. since msb bit for sign.

Take one's complement and add 1 we get 11, and as it is negative number we get answer as -11

The number of full and half-adders required to add 16-bit numbers is- a)8 half-adders, 8 full-adders

- b)1 half-adder, 15 full-adders

- c)16 half-adders, 0 full-adders

- d)4 half-adders, 12 full-adders

Correct answer is option 'B'. Can you explain this answer?

The number of full and half-adders required to add 16-bit numbers is

a)

8 half-adders, 8 full-adders

b)

1 half-adder, 15 full-adders

c)

16 half-adders, 0 full-adders

d)

4 half-adders, 12 full-adders

|

|

Pranab Yadav answered |

for LSB addition we do not need a full adder for addition of subsequent bits we need full adders since carry from previous addition has to be fed into the addition operation

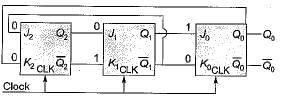

Find the maximum clock frequency at which the counter in the figure below can be operated. Assume that the propagation delay through each flip flop and each AND gate is 10 ns. Also assume that the setup time for the J K inputs of the flip flops is negligible.

Correct answer is '50'. Can you explain this answer?

Find the maximum clock frequency at which the counter in the figure below can be operated. Assume that the propagation delay through each flip flop and each AND gate is 10 ns. Also assume that the setup time for the J K inputs of the flip flops is negligible.

|

|

Yash Patel answered |

In a JK flip flop the output toggles when both J and K inputs are 1. So, we must ensure that with each clock the output from the previous stage reaches the current stage. From the figure, there is an AND gate between each stage and  (10ns for output to reach the gate and 10ns for the output of AND gate to reach the next flipflop) isneeded for the output to reach the next stage. So, minimum time period needed for clock is 20ns which would mean a maximum clock frequency of

(10ns for output to reach the gate and 10ns for the output of AND gate to reach the next flipflop) isneeded for the output to reach the next stage. So, minimum time period needed for clock is 20ns which would mean a maximum clock frequency of

An n stage ripple counter can count up to- a)2n

- b)2n - 1

- c)n

- d)2n-1

Correct answer is option 'B'. Can you explain this answer?

An n stage ripple counter can count up to

a)

2n

b)

2n - 1

c)

n

d)

2n-1

|

|

Sanvi Kapoor answered |

An n stage ripple counter can count up to the binary value represented by the n-bits.

= 2n - 1

= 2n - 1

The total number of Boolean functions which can be realised with four variables is:- a)4

- b)17

- c)256

- d)65,536

Correct answer is option 'D'. Can you explain this answer?

The total number of Boolean functions which can be realised with four variables is:

a)

4

b)

17

c)

256

d)

65,536

|

|

Rhea Reddy answered |

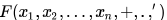

A Boolean function of 4 variables is a function from a set 24 = 16 of elements (all combinations of 4 variables) to a set of 2  elements. So, number of such functions will be 216 = 65,536

elements. So, number of such functions will be 216 = 65,536

The addition of 4-bit, two's complement, binary numbers 1101 and 0100 results in- a)0001 and an overflow

- b)1001 and no overflow

- c)0001 and no overflow

- d)1001 and an overflow

Correct answer is option 'C'. Can you explain this answer?

The addition of 4-bit, two's complement, binary numbers 1101 and 0100 results in

a)

0001 and an overflow

b)

1001 and no overflow

c)

0001 and no overflow

d)

1001 and an overflow

|

Rahul Chatterjee answered |

The addition results in 0001 and no overflow with 1 as carry bit.

In 2's complement addition Overflow happens only when :

- Sign bit of two input numbers is 0, and the result has sign bit 1.

- Sign bit of two input numbers is 1, and the result has sign bit 0.

A positive AND gate is also a negative

- a)NAND gate

- b)OR gate

- c)AND gate

- d)NOR gate

Correct answer is option 'B'. Can you explain this answer?

A positive AND gate is also a negative

a)

NAND gate

b)

OR gate

c)

AND gate

d)

NOR gate

|

|

Niharika Ahuja answered |

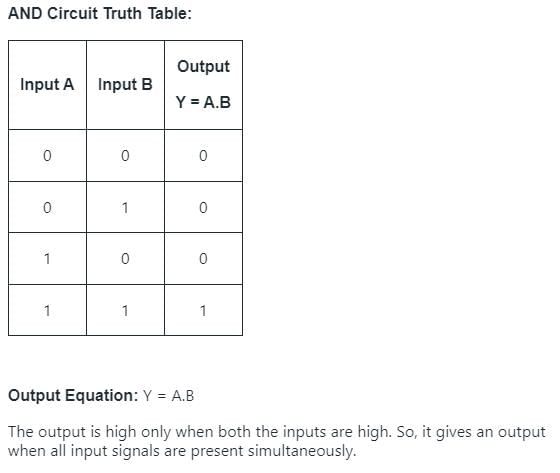

Explanation:

A positive AND gate is a logic gate that produces a HIGH output only when all of its inputs are HIGH. It can be represented by the Boolean expression A.B.

On the other hand, a negative OR gate is a logic gate that produces a LOW output only when all of its inputs are LOW. It can be represented by the Boolean expression A+B.

Now, let's see how a positive AND gate is equivalent to a negative OR gate.

1. NAND gate is not the answer:

A NAND gate is a negative AND gate, which means it produces a LOW output when all of its inputs are HIGH. It can be represented by the Boolean expression A.B. Therefore, a NAND gate is not equivalent to a positive AND gate.

2. AND gate is not the answer:

An AND gate is a positive AND gate, which means it produces a HIGH output only when all of its inputs are HIGH. It can be represented by the Boolean expression A.B. Therefore, an AND gate is the same as a positive AND gate, not a negative OR gate.

3. NOR gate is not the answer:

A NOR gate is a negative OR gate, which means it produces a LOW output only when any of its inputs are HIGH. It can be represented by the Boolean expression A+B. Therefore, a NOR gate is not equivalent to a positive AND gate.

4. OR gate is the answer:

An OR gate is a positive OR gate, which means it produces a HIGH output when any of its inputs are HIGH. It can be represented by the Boolean expression A+B. By using De Morgan's law, we can write the Boolean expression for a negative OR gate as (A.B)'. This is the same as the Boolean expression for a positive AND gate. Therefore, an OR gate is equivalent to a positive AND gate.

Conclusion:

Hence, the correct answer is option B - OR gate.

A positive AND gate is a logic gate that produces a HIGH output only when all of its inputs are HIGH. It can be represented by the Boolean expression A.B.

On the other hand, a negative OR gate is a logic gate that produces a LOW output only when all of its inputs are LOW. It can be represented by the Boolean expression A+B.

Now, let's see how a positive AND gate is equivalent to a negative OR gate.

1. NAND gate is not the answer:

A NAND gate is a negative AND gate, which means it produces a LOW output when all of its inputs are HIGH. It can be represented by the Boolean expression A.B. Therefore, a NAND gate is not equivalent to a positive AND gate.

2. AND gate is not the answer:

An AND gate is a positive AND gate, which means it produces a HIGH output only when all of its inputs are HIGH. It can be represented by the Boolean expression A.B. Therefore, an AND gate is the same as a positive AND gate, not a negative OR gate.

3. NOR gate is not the answer:

A NOR gate is a negative OR gate, which means it produces a LOW output only when any of its inputs are HIGH. It can be represented by the Boolean expression A+B. Therefore, a NOR gate is not equivalent to a positive AND gate.

4. OR gate is the answer:

An OR gate is a positive OR gate, which means it produces a HIGH output when any of its inputs are HIGH. It can be represented by the Boolean expression A+B. By using De Morgan's law, we can write the Boolean expression for a negative OR gate as (A.B)'. This is the same as the Boolean expression for a positive AND gate. Therefore, an OR gate is equivalent to a positive AND gate.

Conclusion:

Hence, the correct answer is option B - OR gate.

What is the result of evaluating the following two expressions using three-digit floating point arithmetic with rounding?(113. + -111.) + 7.51

113. + (-111. + 7.51)- a)9.51 and 10.0 respectively

- b)10.0 and 9.51 respectively

- c)9.51 and 9.51 respectively

- d)10.0 and 10.0 respectively

Correct answer is option 'D'. Can you explain this answer?

What is the result of evaluating the following two expressions using three-digit floating point arithmetic with rounding?

(113. + -111.) + 7.51

113. + (-111. + 7.51)

113. + (-111. + 7.51)

a)

9.51 and 10.0 respectively

b)

10.0 and 9.51 respectively

c)

9.51 and 9.51 respectively

d)

10.0 and 10.0 respectively

|

|

Aditya Deshmukh answered |

The correct answer is a.

(113. + -111.) + 7.51

= 2 + 7.51

= 9.51

113. + (-111. + 7.51)

= 113. + (-111. + 7.51)

= 113. - 103. = 10 [103.49 is rounded to 103.0]

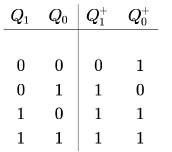

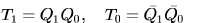

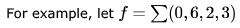

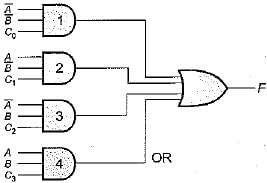

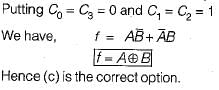

The next state table of a 2-bit saturating up-counter is given below. The counter is built as a synchronous sequential circuit using T flip-flops. The expressions for

The counter is built as a synchronous sequential circuit using T flip-flops. The expressions for  are

are- a)

- b)

- c)

- d)

Correct answer is option 'B'. Can you explain this answer?

The next state table of a 2-bit saturating up-counter is given below.

The counter is built as a synchronous sequential circuit using T flip-flops. The expressions for  are

are

a)

b)

c)

d)

|

|

Yash Patel answered |

By using above excitation table, T1=q1'q0,

T2=(q1q0)'=q1'+q0'

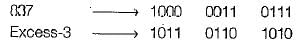

The quantity 837 in excess-3 BCD code would be represented as- a)1001 0011 0111

- b)1000 0001 1001

- c)1011 0110 1010

- d)1000 0011 0111

Correct answer is option 'C'. Can you explain this answer?

The quantity 837 in excess-3 BCD code would be represented as

a)

1001 0011 0111

b)

1000 0001 1001

c)

1011 0110 1010

d)

1000 0011 0111

|

|

Avinash Sharma answered |

The quantity 837 is first converted to BCD representation then it is incremented by 3 bit by bit.

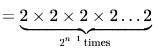

The dual of a Boolean function written as

written as  is the same expression as that of F with + and swapped. F is said to be self-dual if

is the same expression as that of F with + and swapped. F is said to be self-dual if  . The number of self-dual functions with Boolean variables is

. The number of self-dual functions with Boolean variables is- a)

- b)

- c)

- d)

Correct answer is option 'D'. Can you explain this answer?

The dual of a Boolean function written as

written as  is the same expression as that of F with + and swapped. F is said to be self-dual if

is the same expression as that of F with + and swapped. F is said to be self-dual if  . The number of self-dual functions with Boolean variables is

. The number of self-dual functions with Boolean variables is

a)

b)

c)

d)

|

|

Ravi Singh answered |

A function is self dual if it is equal to its dual (A dual function is obtained by interchanging. and +).

For self-dual functions,

1. Number of min terms equals number of max terms

2. Function should not contain two complementary minterms - whose sum equals 2n - 1, where n is the number of variables.

so here (0,7) (1,6) (2,5) (3,4) are complementary terms so in self-dual we can select any one of them but not both. possibility because say from

possibility because say from  we can pick anyone in minterm but not both.

we can pick anyone in minterm but not both.

NOTE:here i have taken only one of the complementary term for min term from the sets.

so remaining numbers will go to MAXTERMS

For above example, 24 = 16 self dual functions are possible

so if we have N variables, total Minterms possible is 2n

then half of them we selected so .

.

and now we have 2 choices for every pair for being selected.

so total such choices

For self-dual functions,

1. Number of min terms equals number of max terms

2. Function should not contain two complementary minterms - whose sum equals 2n - 1, where n is the number of variables.

so here (0,7) (1,6) (2,5) (3,4) are complementary terms so in self-dual we can select any one of them but not both.

NOTE:here i have taken only one of the complementary term for min term from the sets.

so remaining numbers will go to MAXTERMS

For above example, 24 = 16 self dual functions are possible

so if we have N variables, total Minterms possible is 2n

then half of them we selected so

and now we have 2 choices for every pair for being selected.

so total such choices

Assuming all numbers are in 2’s complement representation, which of the following numbers is divisible by 11111011?- a)11100111

- b)11100100

- c)11010111

- d)11011011

Correct answer is option 'A'. Can you explain this answer?

Assuming all numbers are in 2’s complement representation, which of the following numbers is divisible by 11111011?

a)

11100111

b)

11100100

c)

11010111

d)

11011011

|

|

Manasa Dey answered |

MSB of 2's compliment number has a weight of - 2^(n-1).

(Trick: (from reversing sign extension) just skip all leading 1's from MSB expect but 1, and then calculate the value as normal signed binary rep. ) so by calculating, we get the given number is -5 in decimal. and options are

a. -25

b. -28

c. -41

d. -37

Therefore it is clear that - 25 is divisible by - 5. so we can say that (a.) is correct.

(Trick: (from reversing sign extension) just skip all leading 1's from MSB expect but 1, and then calculate the value as normal signed binary rep. ) so by calculating, we get the given number is -5 in decimal. and options are

a. -25

b. -28

c. -41

d. -37

Therefore it is clear that - 25 is divisible by - 5. so we can say that (a.) is correct.

Which of the following input sequences for a cross-coupled R-S flip-flop realized with two NAND gates may lead to an oscillation?- a)11, 00

- b)01, 10

- c)10, 01

- d)00, 11

Correct answer is option 'D'. Can you explain this answer?

Which of the following input sequences for a cross-coupled R-S flip-flop realized with two NAND gates may lead to an oscillation?

a)

11, 00

b)

01, 10

c)

10, 01

d)

00, 11

|

|

Yash Patel answered |

For R-S flip flop with NAND gates (inputs are active low) 11-no change 00-indeterminate..............so option A may make the system oscillate as "00" is the final input. In option D, after "00" flipflop output may oscillate but after "11", it will be stabilized.

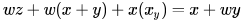

If  are Boolean variables, then which one of the following is INCORRECT?

are Boolean variables, then which one of the following is INCORRECT?- a)

- b)

- c)

- d)

Correct answer is option 'C'. Can you explain this answer?

If  are Boolean variables, then which one of the following is INCORRECT?

are Boolean variables, then which one of the following is INCORRECT?

a)

b)

c)

d)

|

|

Sanvi Kapoor answered |

Option C (wx'(y+xz')+w'.x')y = (wx'y+wx'xz'+w'x')y =

xx' = 0.

So

Wx'y+w'x'y = x'y(w+w') = x'y

xx' = 0.

So

Wx'y+w'x'y = x'y(w+w') = x'y

Consider an eight-bit ripple-carry adder for computing the sum of A and B, where A and B are integers represented in 's complement form. If the decimal value of A is one, the decimal value of B that leads to the longest latency for the sum to stabilize is ___________- a)-1

- b)2

- c) 1

- d) -2

Correct answer is option 'A'. Can you explain this answer?

Consider an eight-bit ripple-carry adder for computing the sum of A and B, where A and B are integers represented in 's complement form. If the decimal value of A is one, the decimal value of B that leads to the longest latency for the sum to stabilize is ___________

a)

-1

b)

2

c)

1

d)

-2

|

|

Neha Choudhury answered |

Here "longest latency for the sum to stabilize" means maximum delay that ripple carry adder would take to add A and B, we are given value of A and need to find the value of B.

The Delay in Ripple Carry Adder is as follows

- For sum there are 2 XOR gates.

- For carry there is 1 XOR,1 AND and 1 OR gate.

i.e total 3 gate delays in case of carry and 2 gate delays in sum.

If we do 2's complement of 1 in 8 bit we get "00000001".

same we do for each option

-1 : "11111111"

2 : "00000010"

1 : "00000001"

-2 : "11111110"

So in case of -1 the carry bit will change and thus it will take 1 extra gate delay, hence we could see that the maximum delay we could get when input at B will be -1, i.e. add “00000001” with “11111111” and would get Maximum delay.

Booth's coding in 8 bits for the decimal number -57 is- a)0-100+1000

- b)0-100+100-1

- c)0-1+100-10+1

- d)00-10+100-1

Correct answer is option 'B'. Can you explain this answer?

Booth's coding in 8 bits for the decimal number -57 is

a)

0-100+1000

b)

0-100+100-1

c)

0-1+100-10+1

d)

00-10+100-1

|

|

Kabir Verma answered |

There are 2 ways for answering This questions.

Way 1 -> Convert 57 to Binary & Get 2's complement. It is "11000111" & Attach one extra 0 to right of it

110001110

Way 1 -> Convert 57 to Binary & Get 2's complement. It is "11000111" & Attach one extra 0 to right of it

110001110

To calculate booth code subtract right digit from left digit in every consecutive 2 digits.

So 11-> 0 , 10 -> +1, .. finally 10 -> +1

So 11-> 0 , 10 -> +1, .. finally 10 -> +1

Simplify Y = AB’ + (A’ + B)C- a)AB’ + C

- b)AB + AC

- c)A’B + AC’

- d)AB + A

Correct answer is option 'A'. Can you explain this answer?

Simplify Y = AB’ + (A’ + B)C

a)

AB’ + C

b)

AB + AC

c)

A’B + AC’

d)

AB + A

|

|

Sanya Agarwal answered |

Y = AB’ + (A’ + B)C = AB’ + (A’ + B)C = AB’ + (AB’)’C = AB’ + C.

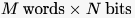

A ROM is used to store the Truth table for a binary multiple unit that will multiply two 4-bit numbers. The size of the ROM  that is required to accommodate the Truth table is

that is required to accommodate the Truth table is  . Write the values of M and N.

. Write the values of M and N.

Correct answer is '8'. Can you explain this answer?

A ROM is used to store the Truth table for a binary multiple unit that will multiply two 4-bit numbers. The size of the ROM  that is required to accommodate the Truth table is

that is required to accommodate the Truth table is  . Write the values of M and N.

. Write the values of M and N.

|

|

Ravi Singh answered |

A is 4 bit binary no A4A3A2A1

B is 4 bit binary no B4B3B2B1

M is result of multiplication M8M7M6M5M4M3M2M1 [check biggest no 1111 x 1111 =11100001]

So 4 bit of A 4 bit of B

input will consist of 8 bit need address 00000000 to 11111111 = 28 address

output will be of 8 bits

so memory will be of

M = 256 , N = 8

B is 4 bit binary no B4B3B2B1

M is result of multiplication M8M7M6M5M4M3M2M1 [check biggest no 1111 x 1111 =11100001]

So 4 bit of A 4 bit of B

input will consist of 8 bit need address 00000000 to 11111111 = 28 address

output will be of 8 bits

so memory will be of

M = 256 , N = 8

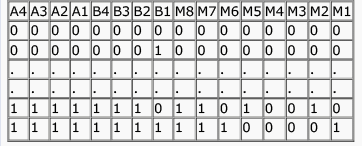

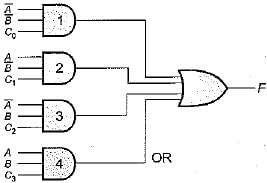

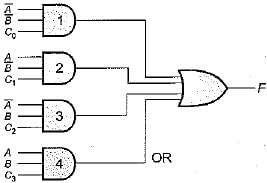

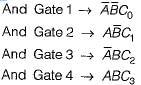

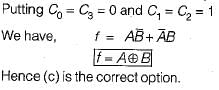

Consider the circuit-shown below. Each of the control inputs, C0 through C3, must be tied to a constant, either ‘0’ or '1'.

What are the values of C0 through C3 that would cause F to be the exclusive OR of A and B?- a)(1 ,0, 0 ,1 )

- b)( 0 ,1 ,1 ,1 )

- c)(0, 1,1,0)

- d)(1,1, 1,1)

Correct answer is option 'C'. Can you explain this answer?

Consider the circuit-shown below. Each of the control inputs, C0 through C3, must be tied to a constant, either ‘0’ or '1'.

What are the values of C0 through C3 that would cause F to be the exclusive OR of A and B?

What are the values of C0 through C3 that would cause F to be the exclusive OR of A and B?

a)

(1 ,0, 0 ,1 )

b)

( 0 ,1 ,1 ,1 )

c)

(0, 1,1,0)

d)

(1,1, 1,1)

|

|

Yash Patel answered |

The output of

Choose the correct alternatives (more than one may be correct) and write the corresponding letters only: The operation which is commutative but not associative is:- a)AND

- b)OR

- c)EX-OR

- d)NAND

Correct answer is option 'D'. Can you explain this answer?

Choose the correct alternatives (more than one may be correct) and write the corresponding letters only: The operation which is commutative but not associative is:

a)

AND

b)

OR

c)

EX-OR

d)

NAND

|

Anjali answered |

Because in NAND gate there is two operation that is NOT & AND .Firstly we perform AND operation which can be COMMUTATIVE.;after this we perform NOT operation which does not hold ASSOCIATIVE property.whereas in all other operations available in option,only one operation are perform so it hold both property.

Let X and Y be the input and Z be the output of a AND gate. The value of Z is given by

- a)X + Y

- b)

- c)X - Y

- d)

Correct answer is option 'B'. Can you explain this answer?

Let X and Y be the input and Z be the output of a AND gate. The value of Z is given by

a)

X + Y

b)

c)

X - Y

d)

|

|

Ananya Kumari answered |

Let x and y be the input and z be the output of a and gate . the value of z is given by

x and y is integers they did negative sign

x- y

x and y is integers they did negative sign

x- y

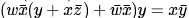

A Boolean function

- a)

- b)

- c)

- d)

Correct answer is option 'D'. Can you explain this answer?

A Boolean function

a)

b)

c)

d)

|

|

Yash Patel answered |

x'y' + x'y = x'(y+y') = x'

x' + xy = x' + y

x' + xy = x' + y

Booth’s algorithm for integer multiplication gives worst performance when the multiplier pattern is- a)101010 ….. 1010

- b)100000 ….. 0001

- c)111111 ….. 1111

- d)011111 ….. 1110

Correct answer is option 'A'. Can you explain this answer?

Booth’s algorithm for integer multiplication gives worst performance when the multiplier pattern is

a)

101010 ….. 1010

b)

100000 ….. 0001

c)

111111 ….. 1111

d)

011111 ….. 1110

|

|

Diya Chauhan answered |

The worst case of an implementation using Booth’s algorithm is when pairs of 01s or 10s occur very frequently in the multiplier.

Let X be the number of distinct 16-bit integers in 2`s complement representation. Let Y be the number of distinct -bit integers in sign magnitude representation Then X Y is______.

Correct answer is '1'. Can you explain this answer?

Let X be the number of distinct 16-bit integers in 2`s complement representation. Let Y be the number of distinct -bit integers in sign magnitude representation Then X Y is______.

|

|

Jaya Chakraborty answered |

For N bits, Distinct values represented in 2's complement is -2n-1 to 2n-1 -1

Distinct values represented in Signed Magnitude is -(2n-1 -1) to 2n-1 -1

Difference is 1.

Distinct values represented in Signed Magnitude is -(2n-1 -1) to 2n-1 -1

Difference is 1.

The number of full and half-adder required to add 16-bit numbers is- a)8 half-adders, 8 full-adders

- b)1 half-adder, 15 full-adders

- c)16 half-adders, 0 full-adders

- d)4 half-adders, 12 full-adders

Correct answer is option 'B'. Can you explain this answer?

The number of full and half-adder required to add 16-bit numbers is

a)

8 half-adders, 8 full-adders

b)

1 half-adder, 15 full-adders

c)

16 half-adders, 0 full-adders

d)

4 half-adders, 12 full-adders

|

|

Kavya Mukherjee answered |

To 16 bits number, 1 half and 15 full address or 16 full address are required.

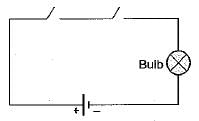

What logic gate is represented by the circuit shown below:

- a)NAND

- b)NOR

- c)AND

- d)EQUIVALENCE

Correct answer is option 'C'. Can you explain this answer?

What logic gate is represented by the circuit shown below:

a)

NAND

b)

NOR

c)

AND

d)

EQUIVALENCE

|

L.03akarshit Raj answered |

And gate because in and gate output will be 1 only and only when both input are 1 .in this case when both switch will on then bulb will on.

Using a 4-bit 2's complement arithmetic, which of the following additions will result in an overflow?

i. 1100 + 1100

ii. 0011 + 0111

iii. 1111 + 0111- a)i only

- b)ii only

- c)iii only

- d)i and iii only

Correct answer is option 'B'. Can you explain this answer?

Using a 4-bit 2's complement arithmetic, which of the following additions will result in an overflow?

i. 1100 + 1100

ii. 0011 + 0111

iii. 1111 + 0111

i. 1100 + 1100

ii. 0011 + 0111

iii. 1111 + 0111

a)

i only

b)

ii only

c)

iii only

d)

i and iii only

|

|

Sounak Joshi answered |

Only (ii) is the answer.

In 2's complement arithmetic, overflow happens only when

1. Sign bit of two input numbers is 0, and the result has sign bit 1

2. Sign bit of two input numbers is 1, and the result has sign bit 0.

Overflow is important only for signed arithmetic while carry is important only for unsigned arithmetic.

A carry happens when there is a carry to (or borrow from) the most significant bit. Here, (i) and (iii) cause a carry but only (ii) causes overflow.

In 2's complement arithmetic, overflow happens only when

1. Sign bit of two input numbers is 0, and the result has sign bit 1

2. Sign bit of two input numbers is 1, and the result has sign bit 0.

Overflow is important only for signed arithmetic while carry is important only for unsigned arithmetic.

A carry happens when there is a carry to (or borrow from) the most significant bit. Here, (i) and (iii) cause a carry but only (ii) causes overflow.

How many pulses are needed to change the contents of a 8-bit up counter from 10101100 to 00100111 (rightmost bit is the LSB)?- a)134

- b)133

- c)124

- d)123

Correct answer is option 'D'. Can you explain this answer?

How many pulses are needed to change the contents of a 8-bit up counter from 10101100 to 00100111 (rightmost bit is the LSB)?

a)

134

b)

133

c)

124

d)

123

|

|

Gargi Sarkar answered |

As in a 28 Counter the range would be from 0-255. Hence to go from 10101100 (172) to 00100111 (39) , the counter has to go initially from 172 to 255 and then from 0 to 39.

Hence to go from 172 to 255, 255-172 = 83 Clock pulses would be required. then from 255 to 0 , again 1 clock pulse would be required.Then from 0 to 39 , 39 clock pulses would be required. Hence in total 83+1+39 =123 Clock pulses would be required.

Hence to go from 172 to 255, 255-172 = 83 Clock pulses would be required. then from 255 to 0 , again 1 clock pulse would be required.Then from 0 to 39 , 39 clock pulses would be required. Hence in total 83+1+39 =123 Clock pulses would be required.

What is the minimum number of gates required to implement the Boolean function (AB+C) if we have to use only 2-input NOR gates?- a)2

- b)3

- c)4

- d)5

Correct answer is option 'B'. Can you explain this answer?

What is the minimum number of gates required to implement the Boolean function (AB+C) if we have to use only 2-input NOR gates?

a)

2

b)

3

c)

4

d)

5

|

|

Rashi Chakraborty answered |

given boolean function is

f = AB + C

= (A+C) . (B +C)

=((A+C)' +(B+C)')'

f = AB + C

= (A+C) . (B +C)

=((A+C)' +(B+C)')'

therefore 3 NOR gate required .

The base (or radix) of the number system such that the following equation holds is____________. 312/20 = 13.1

Correct answer is '5'. Can you explain this answer?

The base (or radix) of the number system such that the following equation holds is____________. 312/20 = 13.1

|

|

Siddharth Pillai answered |

Let ‘x’ be the base or radix of the number system .

The equation is : (3.x2+1.x1+2.x0) /(2.x1 +0.x0) =1.x1 +3.x0 +1.x-1

=>(3.x2+x +2) /(2.x) =x +3 +1/x

=>(3.x2+x +2) /(2.x) =(x2 +3x +1) /x

By solving above quadratic equation you will get x=0 and x=5

As base or radix of a number system cannot be zero, here x = 5

The equation is : (3.x2+1.x1+2.x0) /(2.x1 +0.x0) =1.x1 +3.x0 +1.x-1

=>(3.x2+x +2) /(2.x) =x +3 +1/x

=>(3.x2+x +2) /(2.x) =(x2 +3x +1) /x

By solving above quadratic equation you will get x=0 and x=5

As base or radix of a number system cannot be zero, here x = 5

How many full adders are needed to construct an m-bit parallel adder ;- a)m /2

- b)m

- c)m - 1

- d)m + 1

Correct answer is option 'B'. Can you explain this answer?

How many full adders are needed to construct an m-bit parallel adder ;

a)

m /2

b)

m

c)

m - 1

d)

m + 1

|

|

Akshita Chakraborty answered |

We can construct a m-bit parallel adder by,

(i) m-full adders OR

(ii) (m - 1) full adders and one half adder OR

iii) (2m - 1 ) full adders and (n - 1) OR GATES

(i) m-full adders OR

(ii) (m - 1) full adders and one half adder OR

iii) (2m - 1 ) full adders and (n - 1) OR GATES

It is possible for an enable or strobe input to undergo an expansion of two or more MUX ICs to the digital multiplexer with the proficiency of large number of- a)Inputs

- b)Outputs

- c)Selection lines

- d)All of the Mentioned

Correct answer is option 'A'. Can you explain this answer?

It is possible for an enable or strobe input to undergo an expansion of two or more MUX ICs to the digital multiplexer with the proficiency of large number of

a)

Inputs

b)

Outputs

c)

Selection lines

d)

All of the Mentioned

|

|

Aaditya Ghosh answered |

It is possible for an enable or strobe input to undergo an expansion of two or more MUX ICs to the digital multiplexer with the proficiency of large number of inputs.

Suppose only one multiplexer and one inverter are allowed to be used to implement any Boolean function of variables.

What is the minimum size of the multiplexer needed?- a)2n line to 1 line

- b)2n + 1 line to 1 line

- c)2n - 1 line to 1 line

- d)2n - 2 line to 1 line

Correct answer is option 'C'. Can you explain this answer?

Suppose only one multiplexer and one inverter are allowed to be used to implement any Boolean function of variables.

What is the minimum size of the multiplexer needed?

What is the minimum size of the multiplexer needed?

a)

2n line to 1 line

b)

2n + 1 line to 1 line

c)

2n - 1 line to 1 line

d)

2n - 2 line to 1 line

|

|

Baishali Reddy answered |

2n - 1

We will map variables to select lines and variable to input line

We will map variables to select lines and variable to input line

If 73x (in base-x number system) is equal to 54y (in base y-number system), the possible values of x and y are- a)8, 16

- b)10, 12

- c)9, 13

- d)8, 11

Correct answer is option 'D'. Can you explain this answer?

If 73x (in base-x number system) is equal to 54y (in base y-number system), the possible values of x and y are

a)

8, 16

b)

10, 12

c)

9, 13

d)

8, 11

|

|

Nishanth Roy answered |

x * 7 + 3 = 5 * y + 4 => 7x = 5y + 1. Only option satisfying this is D.

In boolean algebra, the OR operation is performed by which properties?- a)All of the Mentioned

- b)Associative properties

- c)Commutative properties

- d)Distributive properties

Correct answer is option 'A'. Can you explain this answer?

In boolean algebra, the OR operation is performed by which properties?

a)

All of the Mentioned

b)

Associative properties

c)

Commutative properties

d)

Distributive properties

|

|

Sanya Agarwal answered |

The expression for Associative property is given by A + (B + C) = (A + B) + C & A * (B * C) = (A * B) * C.

The expression for Commutative property is given by A + B = B + A & A * B = B * A.

The expression for Distributive property is given by A + BC = (A + B)(A + C) & A(B + C) = AB + AC.

The expression for Commutative property is given by A + B = B + A & A * B = B * A.

The expression for Distributive property is given by A + BC = (A + B)(A + C) & A(B + C) = AB + AC.

The number of 1's in the binary representation of (3*4096 + 15*256 + 5*16 + 3) are:- a)8

- b)9

- c)10

- d)12

Correct answer is option 'C'. Can you explain this answer?

The number of 1's in the binary representation of (3*4096 + 15*256 + 5*16 + 3) are:

a)

8

b)

9

c)

10

d)

12

|

|

Bibek Chakraborty answered |

I suggest following approach , here we can clearly see that numbers are getting multiplied by powers of 16. So this is nothing but Hexadecimal number in disguise.

Convert the following numbers in the given bases into their equivalents in the desired bases:

(110.101)2 = (x)10

Correct answer is '6.625'. Can you explain this answer?

Convert the following numbers in the given bases into their equivalents in the desired bases:

(110.101)2 = (x)10

(110.101)2 = (x)10

|

|

Tanishq Malik answered |

a. 1 * 22 + 1 * 21 + 0 * 20 + 1 * 2-1 + 0 * 2-2 + 1 * 2-3 = 6.625

The octal representation of an integer is (342)8. If this were to be treated as an eight-bit integer in an 8085 based computer, its decimal equivalent is- a)226

- b)-98

- c)76

- d)-30

Correct answer is option 'D'. Can you explain this answer?

The octal representation of an integer is (342)8. If this were to be treated as an eight-bit integer in an 8085 based computer, its decimal equivalent is

a)

226

b)

-98

c)

76

d)

-30

|

|

Shalini Chopra answered |

Octal to Decimal Conversion:

To convert an octal number to decimal, we need to multiply each digit of the octal number with 8 raised to the power of its position from the rightmost digit. Then, we add all the products to get the decimal equivalent of the octal number.

Given octal number is (342)8

So, (342)8 = 3 × 8² + 4 × 8¹ + 2 × 8⁰ = 192 + 32 + 2 = 226

Hence, the decimal equivalent of the given octal number is 226.

Eight-bit Integer in 8085 based Computer:

An eight-bit integer can store a range of numbers from 0 to 255 in binary form. In two's complement representation, the range of numbers is from -128 to 127.

Since the decimal equivalent of the given octal number is 226, which is greater than 127, we need to represent it in two's complement form to fit it into an eight-bit integer in an 8085 based computer.

To convert a positive decimal number to two's complement form, we need to represent the number in binary form and then take its one's complement by changing all 0's to 1's and all 1's to 0's. Then, we add 1 to the one's complement to get the two's complement.

Binary representation of 226 is 11100010.

One's complement of 11100010 is 00011101.

Adding 1 to the one's complement, we get the two's complement as 00011110.

Hence, the two's complement representation of 226 in an eight-bit integer in an 8085 based computer is 00011110.

Decimal Equivalent of Two's Complement:

To find the decimal equivalent of a two's complement number, we need to first check its leftmost bit. If the leftmost bit is 0, then the number is positive and its decimal equivalent is the same as its binary representation. If the leftmost bit is 1, then the number is negative and its decimal equivalent is obtained by taking its one's complement, adding 1 to the one's complement, and then multiplying the result by -1.

In the two's complement representation of 226, the leftmost bit is 0, which means the number is positive.

Hence, the decimal equivalent of the given octal number treated as an eight-bit integer in an 8085 based computer is 226.

To convert an octal number to decimal, we need to multiply each digit of the octal number with 8 raised to the power of its position from the rightmost digit. Then, we add all the products to get the decimal equivalent of the octal number.

Given octal number is (342)8

So, (342)8 = 3 × 8² + 4 × 8¹ + 2 × 8⁰ = 192 + 32 + 2 = 226

Hence, the decimal equivalent of the given octal number is 226.

Eight-bit Integer in 8085 based Computer:

An eight-bit integer can store a range of numbers from 0 to 255 in binary form. In two's complement representation, the range of numbers is from -128 to 127.

Since the decimal equivalent of the given octal number is 226, which is greater than 127, we need to represent it in two's complement form to fit it into an eight-bit integer in an 8085 based computer.

To convert a positive decimal number to two's complement form, we need to represent the number in binary form and then take its one's complement by changing all 0's to 1's and all 1's to 0's. Then, we add 1 to the one's complement to get the two's complement.

Binary representation of 226 is 11100010.

One's complement of 11100010 is 00011101.

Adding 1 to the one's complement, we get the two's complement as 00011110.

Hence, the two's complement representation of 226 in an eight-bit integer in an 8085 based computer is 00011110.

Decimal Equivalent of Two's Complement:

To find the decimal equivalent of a two's complement number, we need to first check its leftmost bit. If the leftmost bit is 0, then the number is positive and its decimal equivalent is the same as its binary representation. If the leftmost bit is 1, then the number is negative and its decimal equivalent is obtained by taking its one's complement, adding 1 to the one's complement, and then multiplying the result by -1.

In the two's complement representation of 226, the leftmost bit is 0, which means the number is positive.

Hence, the decimal equivalent of the given octal number treated as an eight-bit integer in an 8085 based computer is 226.

The exponent of a floating-point number is represented in excess-N code so that:- a)The dynamic range is large.

- b)The precision is high.

- c)The smallest number is represented by all zeros.

- d)Overflow is avoided.

Correct answer is option 'C'. Can you explain this answer?

The exponent of a floating-point number is represented in excess-N code so that:

a)

The dynamic range is large.

b)

The precision is high.

c)

The smallest number is represented by all zeros.

d)

Overflow is avoided.

|

|

Ayush Mukherjee answered |

Excess-N Code Representation

The excess-N code representation is a method used to represent the exponent of a floating-point number. In this representation, a fixed value N is added to the actual exponent value to obtain the excess-N code. This technique is commonly used in computer systems to represent the exponent in floating-point arithmetic.

Dynamic Range

The excess-N code representation allows for a large dynamic range. The dynamic range refers to the range of values that can be represented by the exponent. By using excess-N code, the range of exponents can extend both in the positive and negative directions. This enables the representation of very large and very small numbers, providing a larger dynamic range compared to other representations.

Precision

The precision of a floating-point number refers to the level of detail or accuracy in representing the number. The excess-N code representation does not directly affect the precision of the floating-point number. Precision primarily depends on the mantissa or significand of the floating-point number. However, by using a larger value for N in the excess-N code, the precision can be increased as it allows for a larger range of values to be represented.

Smallest Number Representation

One of the advantages of using excess-N code is that the smallest number can be represented by all zeros. In the excess-N code representation, the value N is chosen such that when it is added to the actual exponent value, it results in a representation with all zeros. This allows for the representation of the smallest possible exponent value without the need for additional bits or special encodings.

Overflow Avoidance

Overflow occurs when the result of an arithmetic operation exceeds the maximum representable value. In floating-point arithmetic, overflow can happen when the exponent becomes too large to be represented. By using excess-N code, the range of representable exponents can be extended, thus avoiding overflow. The excess-N code representation ensures that the exponent can be increased or decreased within the available range, preventing overflow conditions.

In conclusion, the excess-N code representation is used to represent the exponent of a floating-point number. It offers a large dynamic range, allows for high precision by choosing a larger value for N, represents the smallest number with all zeros, and helps avoid overflow conditions. These advantages make excess-N code a commonly used technique in floating-point arithmetic.

The excess-N code representation is a method used to represent the exponent of a floating-point number. In this representation, a fixed value N is added to the actual exponent value to obtain the excess-N code. This technique is commonly used in computer systems to represent the exponent in floating-point arithmetic.

Dynamic Range

The excess-N code representation allows for a large dynamic range. The dynamic range refers to the range of values that can be represented by the exponent. By using excess-N code, the range of exponents can extend both in the positive and negative directions. This enables the representation of very large and very small numbers, providing a larger dynamic range compared to other representations.

Precision

The precision of a floating-point number refers to the level of detail or accuracy in representing the number. The excess-N code representation does not directly affect the precision of the floating-point number. Precision primarily depends on the mantissa or significand of the floating-point number. However, by using a larger value for N in the excess-N code, the precision can be increased as it allows for a larger range of values to be represented.

Smallest Number Representation

One of the advantages of using excess-N code is that the smallest number can be represented by all zeros. In the excess-N code representation, the value N is chosen such that when it is added to the actual exponent value, it results in a representation with all zeros. This allows for the representation of the smallest possible exponent value without the need for additional bits or special encodings.

Overflow Avoidance

Overflow occurs when the result of an arithmetic operation exceeds the maximum representable value. In floating-point arithmetic, overflow can happen when the exponent becomes too large to be represented. By using excess-N code, the range of representable exponents can be extended, thus avoiding overflow. The excess-N code representation ensures that the exponent can be increased or decreased within the available range, preventing overflow conditions.

In conclusion, the excess-N code representation is used to represent the exponent of a floating-point number. It offers a large dynamic range, allows for high precision by choosing a larger value for N, represents the smallest number with all zeros, and helps avoid overflow conditions. These advantages make excess-N code a commonly used technique in floating-point arithmetic.

The 2's complement representation of (-539)10 in hexadecimal is- a)ABE

- b)DBC

- c)DE5

- d)9E7

Correct answer is option 'C'. Can you explain this answer?

The 2's complement representation of (-539)10 in hexadecimal is

a)

ABE

b)

DBC

c)

DE5

d)

9E7

|

|

Bibek Chakraborty answered |

539 = 512 + 16 + 8 + 2 + 1 = 29 + 24 + 23 + 21 + 20

= (1000011011)2

Now all answers have 12 bits, so we add two 0's at beginning = (001000011011)2

To convert to 2's complement invert all bits till the rightmost 1, which will be (110111100101)2

= (1101 1110 0101)2

= (DE5)16

= (1000011011)2

Now all answers have 12 bits, so we add two 0's at beginning = (001000011011)2

To convert to 2's complement invert all bits till the rightmost 1, which will be (110111100101)2

= (1101 1110 0101)2

= (DE5)16

For what logic gate, the output is complement of the input?- a)NOT

- b)AND

- c)OR

- d)XOR

Correct answer is option 'A'. Can you explain this answer?

For what logic gate, the output is complement of the input?

a)

NOT

b)

AND

c)

OR

d)

XOR

|

|

Rajesh Mukherjee answered |

By using NOT gate output is complement of input

Let an an-1 ... a1 a0 be the binary representation of an integer b. The integer b is divisible by 3 if- a)The number of one’s is divisible by 3

- b)The number of one’s divisible by 3, but bof by 9

- c)The number of zeroes is divisible 3

- d)The difference of alternate sum, i.e., (a0,+a2+...) - a1+a3+...) is divided by 3

Correct answer is option 'D'. Can you explain this answer?

Let an an-1 ... a1 a0 be the binary representation of an integer b. The integer b is divisible by 3 if

a)

The number of one’s is divisible by 3

b)

The number of one’s divisible by 3, but bof by 9

c)

The number of zeroes is divisible 3

d)

The difference of alternate sum, i.e., (a0,+a2+...) - a1+a3+...) is divided by 3

|

|

Saikat Basu answered |

Binary representation of 12 is 110 D

So, (q0 + q2)-{q1 + q3)

= (0 + 1)- ( 0 + 1)

= 1 - 1

= 0

0 is divisible by 3 so, true.

So, (q0 + q2)-{q1 + q3)

= (0 + 1)- ( 0 + 1)

= 1 - 1

= 0

0 is divisible by 3 so, true.

The smallest integer that can be represented by an 8-bit number in 2's complement form is- a)-256

- b)-128

- c)-127

- d)0

Correct answer is option 'B'. Can you explain this answer?

The smallest integer that can be represented by an 8-bit number in 2's complement form is

a)

-256

b)

-128

c)

-127

d)

0

|

|

Hrishikesh Unni answered |

Range of 2's compliment no = > (- 2n-1)to + (2n-1 - 1)

Here n = No of bits = 8.

So minimum no = -2 ^ 7 = (B) -128

Here n = No of bits = 8.

So minimum no = -2 ^ 7 = (B) -128

An N-bit carry lookahead adder, where N is a multiple of 4, employs ICs 74181 (4 bit ALU) and 74182 ( 4 bit carry lookahead generator).

The minimum addition time using the best architecture for this adder is- a)proportional to N

- b)proportional to log N

- c)a constant

- d)None of the above

Correct answer is option 'B'. Can you explain this answer?

An N-bit carry lookahead adder, where N is a multiple of 4, employs ICs 74181 (4 bit ALU) and 74182 ( 4 bit carry lookahead generator).

The minimum addition time using the best architecture for this adder is

The minimum addition time using the best architecture for this adder is

a)

proportional to N

b)

proportional to log N

c)

a constant

d)

None of the above

|

|

Diya Chauhan answered |

For N = 64 bits

Suppose you want to build a 64 bit adder then you need 16 4-bit ALU and 16 4-bit carry generator, at this point there will be 16 carries that will ripple through these 16 ALU modules, to speed up the adder we need to get rid of these 16 rippling carries, now we can again use 4 4-bit carry generator to generate these 16 carries, now we have only 4 carries to ripple through, again we can use the same trick to minimize the rippling of these 4 carries, we can use an additional 4-bit carry generator which will generate these carry and we are done :) there will be no more propagation of carry among the ALU modules.

So the we have used 3 level of 4-bit carry generator, and the time taken to add 64 bits will be proportional to 3 which is log464.

So in general to add N-bits it takes Log4N time.

Suppose you want to build a 64 bit adder then you need 16 4-bit ALU and 16 4-bit carry generator, at this point there will be 16 carries that will ripple through these 16 ALU modules, to speed up the adder we need to get rid of these 16 rippling carries, now we can again use 4 4-bit carry generator to generate these 16 carries, now we have only 4 carries to ripple through, again we can use the same trick to minimize the rippling of these 4 carries, we can use an additional 4-bit carry generator which will generate these carry and we are done :) there will be no more propagation of carry among the ALU modules.

So the we have used 3 level of 4-bit carry generator, and the time taken to add 64 bits will be proportional to 3 which is log464.

So in general to add N-bits it takes Log4N time.

The representation of the value of a 16 - bit unsigned integer X in hexadecimal number system is BC A9. The representation of the value of X in octal number system is- a)571244

- b)736251

- c)571247

- d)136251

Correct answer is option 'D'. Can you explain this answer?

The representation of the value of a 16 - bit unsigned integer X in hexadecimal number system is BC A9. The representation of the value of X in octal number system is

a)

571244

b)

736251

c)

571247

d)

136251

|

|

Subham Saha answered |

Representation of a 16-bit unsigned integer X in hexadecimal number system is BC A9. We need to find the representation of this value in the octal number system.

To convert a hexadecimal number to an octal number, we can follow these steps:

1. Convert the hexadecimal number to binary.

2. Group the binary digits into groups of three from right to left.

3. Convert each group of three binary digits to its octal equivalent.

4. Combine the octal digits to get the final octal representation.

Let's apply these steps to the given hexadecimal number BC A9:

1. Convert hexadecimal to binary:

BC = 1011 1100

A9 = 1010 1001

2. Group the binary digits into groups of three:

1011 1100 = 101 111 00

1010 1001 = 101 010 01

3. Convert each group of three binary digits to octal:

101 = 5

111 = 7

00 = 0

101 = 5

010 = 2

01 = 1

4. Combine the octal digits:

570251

Therefore, the representation of the value of X in the octal number system is 570251.

Now, let's check the options given:

a) 571244: This is not the correct answer as it does not match the calculated octal representation.

b) 736251: This is not the correct answer as it does not match the calculated octal representation.

c) 571247: This is not the correct answer as it does not match the calculated octal representation.

d) 136251: This is the correct answer as it matches the calculated octal representation.

Hence, the correct answer is option 'D' (136251).

To convert a hexadecimal number to an octal number, we can follow these steps:

1. Convert the hexadecimal number to binary.

2. Group the binary digits into groups of three from right to left.

3. Convert each group of three binary digits to its octal equivalent.

4. Combine the octal digits to get the final octal representation.

Let's apply these steps to the given hexadecimal number BC A9:

1. Convert hexadecimal to binary:

BC = 1011 1100

A9 = 1010 1001

2. Group the binary digits into groups of three:

1011 1100 = 101 111 00

1010 1001 = 101 010 01

3. Convert each group of three binary digits to octal:

101 = 5

111 = 7

00 = 0

101 = 5

010 = 2

01 = 1

4. Combine the octal digits:

570251

Therefore, the representation of the value of X in the octal number system is 570251.

Now, let's check the options given:

a) 571244: This is not the correct answer as it does not match the calculated octal representation.

b) 736251: This is not the correct answer as it does not match the calculated octal representation.

c) 571247: This is not the correct answer as it does not match the calculated octal representation.

d) 136251: This is the correct answer as it matches the calculated octal representation.

Hence, the correct answer is option 'D' (136251).

Zero has two representations in- a)Sign magnitude

- b)2's complement

- c)1's complement

- d)None of the above

Correct answer is option 'A,C'. Can you explain this answer?

Zero has two representations in

a)

Sign magnitude

b)

2's complement

c)

1's complement

d)

None of the above

|

|

Samarth Kapoor answered |

Sign Magnitude

+0 = 0000

-0 = 1000

1's complement

+0 = 0000

-0 = 1111

+0 = 0000

-0 = 1000

1's complement

+0 = 0000

-0 = 1111

Latches constructed with NOR and NAND gates tend to remain in the latched condition due to which configuration feature?- a)Low input voltages

- b)Synchronous operation

- c)Gate impedance

- d)Cross coupling

Correct answer is option 'D'. Can you explain this answer?

Latches constructed with NOR and NAND gates tend to remain in the latched condition due to which configuration feature?

a)

Low input voltages

b)

Synchronous operation

c)

Gate impedance

d)

Cross coupling

|

|

Gargi Sarkar answered |

Both inputs of a latch are directly connected to the other’s output. Such types of structure is called cross coupling and due to which latches remain in the latched condition.

Chapter doubts & questions for Digital Logic - GATE Computer Science Engineering(CSE) 2026 Mock Test Series 2025 is part of Computer Science Engineering (CSE) exam preparation. The chapters have been prepared according to the Computer Science Engineering (CSE) exam syllabus. The Chapter doubts & questions, notes, tests & MCQs are made for Computer Science Engineering (CSE) 2025 Exam. Find important definitions, questions, notes, meanings, examples, exercises, MCQs and online tests here.

Chapter doubts & questions of Digital Logic - GATE Computer Science Engineering(CSE) 2026 Mock Test Series in English & Hindi are available as part of Computer Science Engineering (CSE) exam.

Download more important topics, notes, lectures and mock test series for Computer Science Engineering (CSE) Exam by signing up for free.

Contact Support

Our team is online on weekdays between 10 AM - 7 PM

Typical reply within 3 hours

|

Free Exam Preparation

at your Fingertips!

Access Free Study Material - Test Series, Structured Courses, Free Videos & Study Notes and Prepare for Your Exam With Ease

Join the 10M+ students on EduRev

Join the 10M+ students on EduRev

|

|

Create your account for free

OR

Forgot Password

OR

Signup to see your scores

go up

within 7 days!

within 7 days!

Takes less than 10 seconds to signup