Computer Science Engineering (CSE) Exam > Computer Science Engineering (CSE) Questions > A 5 stage pipeline is used to overlap all the...

Start Learning for Free

A 5 stage pipeline is used to overlap all the instructions except the branch instructions. The target of the branch can’t be fetched till the current instruction is completed. What is throughput of the system if 20% of instructions are branch instructions? Ignore the overhead of buffer register. Each stage is having same amount delay. The pipeline clock is 10 ns. Branch penalty is of 4 cycles.

- a)55 MIPS

- b)45 MIPS

- c)65 MIPS

- d)None of these

Correct answer is option 'A'. Can you explain this answer?

Verified Answer

A 5 stage pipeline is used to overlap all the instructions except the ...

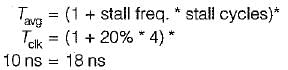

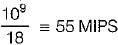

∴ Throughput = Number of instructions executed/ sec

18 ns ........... one instruction

109 ns ......... ?

⇒

Most Upvoted Answer

A 5 stage pipeline is used to overlap all the instructions except the ...

Be calculated and the branch instruction can be fetched and decoded in the first stage of the pipeline. However, the actual branching decision cannot be made until the branch instruction reaches the execution stage in the pipeline. This is because the branch target address is not known until the branch instruction is executed.

In a 5-stage pipeline, the stages are typically as follows:

1. Instruction Fetch (IF): Fetch the next instruction from memory.

2. Instruction Decode (ID): Decode the fetched instruction and read the necessary register values.

3. Execute (EX): Perform the necessary calculations or operations based on the decoded instruction.

4. Memory Access (MEM): Access memory if necessary, such as loading or storing data.

5. Write Back (WB): Write the result of the instruction back to the appropriate register.

In the case of a branch instruction, the target address is calculated in the EX stage and the actual branching decision is made in the MEM stage. If the branch is taken, the pipeline needs to be flushed and the fetched instructions after the branch are discarded. The new target address is then used to fetch the next instruction after the branch.

By overlapping the execution of instructions in the pipeline, the processor can achieve higher instruction throughput and improve overall performance. However, branch instructions introduce a challenge because the target address is not known until the branch instruction is executed. To minimize the impact of branches on pipeline performance, techniques such as branch prediction and speculative execution are used.

In a 5-stage pipeline, the stages are typically as follows:

1. Instruction Fetch (IF): Fetch the next instruction from memory.

2. Instruction Decode (ID): Decode the fetched instruction and read the necessary register values.

3. Execute (EX): Perform the necessary calculations or operations based on the decoded instruction.

4. Memory Access (MEM): Access memory if necessary, such as loading or storing data.

5. Write Back (WB): Write the result of the instruction back to the appropriate register.

In the case of a branch instruction, the target address is calculated in the EX stage and the actual branching decision is made in the MEM stage. If the branch is taken, the pipeline needs to be flushed and the fetched instructions after the branch are discarded. The new target address is then used to fetch the next instruction after the branch.

By overlapping the execution of instructions in the pipeline, the processor can achieve higher instruction throughput and improve overall performance. However, branch instructions introduce a challenge because the target address is not known until the branch instruction is executed. To minimize the impact of branches on pipeline performance, techniques such as branch prediction and speculative execution are used.

|

Explore Courses for Computer Science Engineering (CSE) exam

|

|

Question Description

A 5 stage pipeline is used to overlap all the instructions except the branch instructions. The target of the branch can’t be fetched till the current instruction is completed. What is throughput of the system if 20% of instructions are branch instructions? Ignore the overhead of buffer register. Each stage is having same amount delay. The pipeline clock is 10 ns. Branch penalty is of 4 cycles.a)55 MIPSb)45 MIPSc)65 MIPSd)None of theseCorrect answer is option 'A'. Can you explain this answer? for Computer Science Engineering (CSE) 2025 is part of Computer Science Engineering (CSE) preparation. The Question and answers have been prepared according to the Computer Science Engineering (CSE) exam syllabus. Information about A 5 stage pipeline is used to overlap all the instructions except the branch instructions. The target of the branch can’t be fetched till the current instruction is completed. What is throughput of the system if 20% of instructions are branch instructions? Ignore the overhead of buffer register. Each stage is having same amount delay. The pipeline clock is 10 ns. Branch penalty is of 4 cycles.a)55 MIPSb)45 MIPSc)65 MIPSd)None of theseCorrect answer is option 'A'. Can you explain this answer? covers all topics & solutions for Computer Science Engineering (CSE) 2025 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for A 5 stage pipeline is used to overlap all the instructions except the branch instructions. The target of the branch can’t be fetched till the current instruction is completed. What is throughput of the system if 20% of instructions are branch instructions? Ignore the overhead of buffer register. Each stage is having same amount delay. The pipeline clock is 10 ns. Branch penalty is of 4 cycles.a)55 MIPSb)45 MIPSc)65 MIPSd)None of theseCorrect answer is option 'A'. Can you explain this answer?.

A 5 stage pipeline is used to overlap all the instructions except the branch instructions. The target of the branch can’t be fetched till the current instruction is completed. What is throughput of the system if 20% of instructions are branch instructions? Ignore the overhead of buffer register. Each stage is having same amount delay. The pipeline clock is 10 ns. Branch penalty is of 4 cycles.a)55 MIPSb)45 MIPSc)65 MIPSd)None of theseCorrect answer is option 'A'. Can you explain this answer? for Computer Science Engineering (CSE) 2025 is part of Computer Science Engineering (CSE) preparation. The Question and answers have been prepared according to the Computer Science Engineering (CSE) exam syllabus. Information about A 5 stage pipeline is used to overlap all the instructions except the branch instructions. The target of the branch can’t be fetched till the current instruction is completed. What is throughput of the system if 20% of instructions are branch instructions? Ignore the overhead of buffer register. Each stage is having same amount delay. The pipeline clock is 10 ns. Branch penalty is of 4 cycles.a)55 MIPSb)45 MIPSc)65 MIPSd)None of theseCorrect answer is option 'A'. Can you explain this answer? covers all topics & solutions for Computer Science Engineering (CSE) 2025 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for A 5 stage pipeline is used to overlap all the instructions except the branch instructions. The target of the branch can’t be fetched till the current instruction is completed. What is throughput of the system if 20% of instructions are branch instructions? Ignore the overhead of buffer register. Each stage is having same amount delay. The pipeline clock is 10 ns. Branch penalty is of 4 cycles.a)55 MIPSb)45 MIPSc)65 MIPSd)None of theseCorrect answer is option 'A'. Can you explain this answer?.

Solutions for A 5 stage pipeline is used to overlap all the instructions except the branch instructions. The target of the branch can’t be fetched till the current instruction is completed. What is throughput of the system if 20% of instructions are branch instructions? Ignore the overhead of buffer register. Each stage is having same amount delay. The pipeline clock is 10 ns. Branch penalty is of 4 cycles.a)55 MIPSb)45 MIPSc)65 MIPSd)None of theseCorrect answer is option 'A'. Can you explain this answer? in English & in Hindi are available as part of our courses for Computer Science Engineering (CSE).

Download more important topics, notes, lectures and mock test series for Computer Science Engineering (CSE) Exam by signing up for free.

Here you can find the meaning of A 5 stage pipeline is used to overlap all the instructions except the branch instructions. The target of the branch can’t be fetched till the current instruction is completed. What is throughput of the system if 20% of instructions are branch instructions? Ignore the overhead of buffer register. Each stage is having same amount delay. The pipeline clock is 10 ns. Branch penalty is of 4 cycles.a)55 MIPSb)45 MIPSc)65 MIPSd)None of theseCorrect answer is option 'A'. Can you explain this answer? defined & explained in the simplest way possible. Besides giving the explanation of

A 5 stage pipeline is used to overlap all the instructions except the branch instructions. The target of the branch can’t be fetched till the current instruction is completed. What is throughput of the system if 20% of instructions are branch instructions? Ignore the overhead of buffer register. Each stage is having same amount delay. The pipeline clock is 10 ns. Branch penalty is of 4 cycles.a)55 MIPSb)45 MIPSc)65 MIPSd)None of theseCorrect answer is option 'A'. Can you explain this answer?, a detailed solution for A 5 stage pipeline is used to overlap all the instructions except the branch instructions. The target of the branch can’t be fetched till the current instruction is completed. What is throughput of the system if 20% of instructions are branch instructions? Ignore the overhead of buffer register. Each stage is having same amount delay. The pipeline clock is 10 ns. Branch penalty is of 4 cycles.a)55 MIPSb)45 MIPSc)65 MIPSd)None of theseCorrect answer is option 'A'. Can you explain this answer? has been provided alongside types of A 5 stage pipeline is used to overlap all the instructions except the branch instructions. The target of the branch can’t be fetched till the current instruction is completed. What is throughput of the system if 20% of instructions are branch instructions? Ignore the overhead of buffer register. Each stage is having same amount delay. The pipeline clock is 10 ns. Branch penalty is of 4 cycles.a)55 MIPSb)45 MIPSc)65 MIPSd)None of theseCorrect answer is option 'A'. Can you explain this answer? theory, EduRev gives you an

ample number of questions to practice A 5 stage pipeline is used to overlap all the instructions except the branch instructions. The target of the branch can’t be fetched till the current instruction is completed. What is throughput of the system if 20% of instructions are branch instructions? Ignore the overhead of buffer register. Each stage is having same amount delay. The pipeline clock is 10 ns. Branch penalty is of 4 cycles.a)55 MIPSb)45 MIPSc)65 MIPSd)None of theseCorrect answer is option 'A'. Can you explain this answer? tests, examples and also practice Computer Science Engineering (CSE) tests.

|

Explore Courses for Computer Science Engineering (CSE) exam

|

|

Signup for Free!

Signup to see your scores go up within 7 days! Learn & Practice with 1000+ FREE Notes, Videos & Tests.