Electrical Engineering (EE) Exam > Electrical Engineering (EE) Questions > Assertion (A): The indeterminate condition of...

Start Learning for Free

Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.

Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.

Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.

- a)Both A and R are true and R is the correct explanation of A.

- b)Both A and R are true but R is not the correct explanation of A.

- c)A is true but R is false.

- d)A is false but R is true

Correct answer is option 'D'. Can you explain this answer?

| FREE This question is part of | Download PDF Attempt this Test |

Verified Answer

Assertion (A): The indeterminate condition of the J-K flip-flop is per...

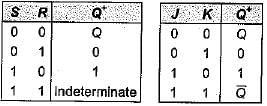

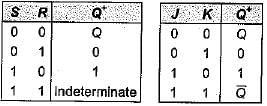

The truth table for S-ffand J-Kflip-flop are shown below.

It is clear from the above truth table that when S = R = 1, the output of S-R flip-flop is indeterminate. However, when J = K = 1, the output of J-Kflip-flop is (not indeterminate). Therefore, the indeterminate condition of the S-R flip-flop is permitted in a J-Kflip-flop.

(not indeterminate). Therefore, the indeterminate condition of the S-R flip-flop is permitted in a J-Kflip-flop.

A J-Kflip-flop has a characteristic similar to that of an S-R flip-flop which is evident from the above truth tables.

Hence, assertion is false but reason is true.

It is clear from the above truth table that when S = R = 1, the output of S-R flip-flop is indeterminate. However, when J = K = 1, the output of J-Kflip-flop is

(not indeterminate). Therefore, the indeterminate condition of the S-R flip-flop is permitted in a J-Kflip-flop.

(not indeterminate). Therefore, the indeterminate condition of the S-R flip-flop is permitted in a J-Kflip-flop.A J-Kflip-flop has a characteristic similar to that of an S-R flip-flop which is evident from the above truth tables.

Hence, assertion is false but reason is true.

Most Upvoted Answer

Assertion (A): The indeterminate condition of the J-K flip-flop is per...

Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in the S-R flip-flop.

Reason (R): A J-K flip-flop has a characteristic similar to that of an S-R flip-flop.

The correct answer is option 'D', which states that Assertion (A) is false but Reason (R) is true.

Explanation:

Understanding Flip-Flops:

- Flip-flops are sequential logic circuits that can store one bit of information.

- They are commonly used in digital systems for data storage, synchronization, and control.

- Different types of flip-flops include S-R flip-flop, J-K flip-flop, D flip-flop, and T flip-flop.

S-R Flip-Flop:

- The S-R flip-flop (Set-Reset flip-flop) is a basic type of flip-flop.

- It has two inputs: Set (S) and Reset (R).

- The S-R flip-flop has two stable states: Set (Q=1) and Reset (Q=0).

- The outputs Q and Q' are complementary to each other.

- When S=0 and R=0, the flip-flop remains in its current state.

- When S=1 and R=0, the flip-flop is set (Q=1).

- When S=0 and R=1, the flip-flop is reset (Q=0).

- When S=1 and R=1, the flip-flop enters an indeterminate state, where the outputs are unpredictable.

J-K Flip-Flop:

- The J-K flip-flop is an extension of the S-R flip-flop.

- It has two additional inputs: J (Jack) and K (King).

- The J-K flip-flop also has two stable states: Set (Q=1) and Reset (Q=0).

- The J-K flip-flop has the advantage of eliminating the indeterminate state of the S-R flip-flop.

- When J=0 and K=0, the flip-flop remains in its current state.

- When J=1 and K=0, the flip-flop is set (Q=1).

- When J=0 and K=1, the flip-flop is reset (Q=0).

- When J=1 and K=1, the flip-flop toggles its state (Q' = Q').

Difference between S-R Flip-Flop and J-K Flip-Flop:

- In an S-R flip-flop, when both inputs are set to 1, the outputs enter an indeterminate state.

- This means that the outputs can be unpredictable, leading to unreliable behavior.

- In a J-K flip-flop, when both inputs are set to 1, the flip-flop toggles its state.

- This eliminates the indeterminate state and ensures reliable behavior.

Conclusion:

- The indeterminate condition of the J-K flip-flop is not permitted in the S-R flip-flop.

- The J-K flip-flop has a characteristic (toggling) that is not present in the S-R flip-flop.

- Therefore, Assertion (A) is false but Reason (R) is true.

Reason (R): A J-K flip-flop has a characteristic similar to that of an S-R flip-flop.

The correct answer is option 'D', which states that Assertion (A) is false but Reason (R) is true.

Explanation:

Understanding Flip-Flops:

- Flip-flops are sequential logic circuits that can store one bit of information.

- They are commonly used in digital systems for data storage, synchronization, and control.

- Different types of flip-flops include S-R flip-flop, J-K flip-flop, D flip-flop, and T flip-flop.

S-R Flip-Flop:

- The S-R flip-flop (Set-Reset flip-flop) is a basic type of flip-flop.

- It has two inputs: Set (S) and Reset (R).

- The S-R flip-flop has two stable states: Set (Q=1) and Reset (Q=0).

- The outputs Q and Q' are complementary to each other.

- When S=0 and R=0, the flip-flop remains in its current state.

- When S=1 and R=0, the flip-flop is set (Q=1).

- When S=0 and R=1, the flip-flop is reset (Q=0).

- When S=1 and R=1, the flip-flop enters an indeterminate state, where the outputs are unpredictable.

J-K Flip-Flop:

- The J-K flip-flop is an extension of the S-R flip-flop.

- It has two additional inputs: J (Jack) and K (King).

- The J-K flip-flop also has two stable states: Set (Q=1) and Reset (Q=0).

- The J-K flip-flop has the advantage of eliminating the indeterminate state of the S-R flip-flop.

- When J=0 and K=0, the flip-flop remains in its current state.

- When J=1 and K=0, the flip-flop is set (Q=1).

- When J=0 and K=1, the flip-flop is reset (Q=0).

- When J=1 and K=1, the flip-flop toggles its state (Q' = Q').

Difference between S-R Flip-Flop and J-K Flip-Flop:

- In an S-R flip-flop, when both inputs are set to 1, the outputs enter an indeterminate state.

- This means that the outputs can be unpredictable, leading to unreliable behavior.

- In a J-K flip-flop, when both inputs are set to 1, the flip-flop toggles its state.

- This eliminates the indeterminate state and ensures reliable behavior.

Conclusion:

- The indeterminate condition of the J-K flip-flop is not permitted in the S-R flip-flop.

- The J-K flip-flop has a characteristic (toggling) that is not present in the S-R flip-flop.

- Therefore, Assertion (A) is false but Reason (R) is true.

Attention Electrical Engineering (EE) Students!

To make sure you are not studying endlessly, EduRev has designed Electrical Engineering (EE) study material, with Structured Courses, Videos, & Test Series. Plus get personalized analysis, doubt solving and improvement plans to achieve a great score in Electrical Engineering (EE).

|

Explore Courses for Electrical Engineering (EE) exam

|

|

Similar Electrical Engineering (EE) Doubts

Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.a)Both A and R are true and R is the correct explanation of A.b)Both A and R are true but R is not the correct explanation of A.c)A is true but R is false.d)A is false but R is trueCorrect answer is option 'D'. Can you explain this answer?

Question Description

Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.a)Both A and R are true and R is the correct explanation of A.b)Both A and R are true but R is not the correct explanation of A.c)A is true but R is false.d)A is false but R is trueCorrect answer is option 'D'. Can you explain this answer? for Electrical Engineering (EE) 2024 is part of Electrical Engineering (EE) preparation. The Question and answers have been prepared according to the Electrical Engineering (EE) exam syllabus. Information about Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.a)Both A and R are true and R is the correct explanation of A.b)Both A and R are true but R is not the correct explanation of A.c)A is true but R is false.d)A is false but R is trueCorrect answer is option 'D'. Can you explain this answer? covers all topics & solutions for Electrical Engineering (EE) 2024 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.a)Both A and R are true and R is the correct explanation of A.b)Both A and R are true but R is not the correct explanation of A.c)A is true but R is false.d)A is false but R is trueCorrect answer is option 'D'. Can you explain this answer?.

Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.a)Both A and R are true and R is the correct explanation of A.b)Both A and R are true but R is not the correct explanation of A.c)A is true but R is false.d)A is false but R is trueCorrect answer is option 'D'. Can you explain this answer? for Electrical Engineering (EE) 2024 is part of Electrical Engineering (EE) preparation. The Question and answers have been prepared according to the Electrical Engineering (EE) exam syllabus. Information about Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.a)Both A and R are true and R is the correct explanation of A.b)Both A and R are true but R is not the correct explanation of A.c)A is true but R is false.d)A is false but R is trueCorrect answer is option 'D'. Can you explain this answer? covers all topics & solutions for Electrical Engineering (EE) 2024 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.a)Both A and R are true and R is the correct explanation of A.b)Both A and R are true but R is not the correct explanation of A.c)A is true but R is false.d)A is false but R is trueCorrect answer is option 'D'. Can you explain this answer?.

Solutions for Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.a)Both A and R are true and R is the correct explanation of A.b)Both A and R are true but R is not the correct explanation of A.c)A is true but R is false.d)A is false but R is trueCorrect answer is option 'D'. Can you explain this answer? in English & in Hindi are available as part of our courses for Electrical Engineering (EE).

Download more important topics, notes, lectures and mock test series for Electrical Engineering (EE) Exam by signing up for free.

Here you can find the meaning of Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.a)Both A and R are true and R is the correct explanation of A.b)Both A and R are true but R is not the correct explanation of A.c)A is true but R is false.d)A is false but R is trueCorrect answer is option 'D'. Can you explain this answer? defined & explained in the simplest way possible. Besides giving the explanation of

Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.a)Both A and R are true and R is the correct explanation of A.b)Both A and R are true but R is not the correct explanation of A.c)A is true but R is false.d)A is false but R is trueCorrect answer is option 'D'. Can you explain this answer?, a detailed solution for Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.a)Both A and R are true and R is the correct explanation of A.b)Both A and R are true but R is not the correct explanation of A.c)A is true but R is false.d)A is false but R is trueCorrect answer is option 'D'. Can you explain this answer? has been provided alongside types of Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.a)Both A and R are true and R is the correct explanation of A.b)Both A and R are true but R is not the correct explanation of A.c)A is true but R is false.d)A is false but R is trueCorrect answer is option 'D'. Can you explain this answer? theory, EduRev gives you an

ample number of questions to practice Assertion (A): The indeterminate condition of the J-K flip-flop is permitted in S-R flip-flop.Reason (R): A J-Kfiip-flop has a characteristic similar to that of an S-R flip-flop.a)Both A and R are true and R is the correct explanation of A.b)Both A and R are true but R is not the correct explanation of A.c)A is true but R is false.d)A is false but R is trueCorrect answer is option 'D'. Can you explain this answer? tests, examples and also practice Electrical Engineering (EE) tests.

|

Explore Courses for Electrical Engineering (EE) exam

|

|

Suggested Free Tests

Signup for Free!

Signup to see your scores go up within 7 days! Learn & Practice with 1000+ FREE Notes, Videos & Tests.