Electrical Engineering (EE) Exam > Electrical Engineering (EE) Questions > In CMOS designs, why size of PMOS is kept lar...

Start Learning for Free

In CMOS designs, why size of PMOS is kept larger than size of NMOS?

- a)To get higher drive strength

- b)To reduce power dissipation

- c)To get balanced rise/fall time

- d)All of above

Correct answer is option 'C'. Can you explain this answer?

Most Upvoted Answer

In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)T...

To maximize the switching speed of a logic gate, for example, an inverter, it is best if the rise and fall time of the logic gate’s output signal is the same.

For this to occur, the top side transistors of the logic gate must switch current into the output of the logic gate at the same magnitude as the low side transistors.

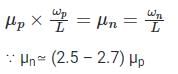

Since PMOS transistors (high side) have approximately half the mobility of NMOS transistors (low side), it is necessary to add two parallel PMOS devices to the high side to achieve the equivalent magnitude currents.

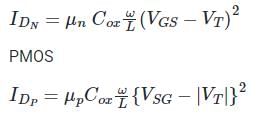

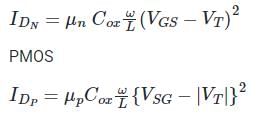

In saturation

NMOS:

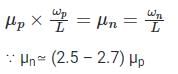

Cox and voltage are the same for both side, when

Considering the same length as it is a fixed constraint for the circuit.

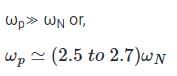

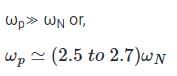

that’s why we take PMOS size greater than N-MOS

NMOS:

Cox and voltage are the same for both side, when

Considering the same length as it is a fixed constraint for the circuit.

that’s why we take PMOS size greater than N-MOS

Free Test

FREE

| Start Free Test |

Community Answer

In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)T...

Introduction:

In CMOS designs, the size of PMOS (p-channel metal-oxide-semiconductor) transistors is typically kept larger than the size of NMOS (n-channel metal-oxide-semiconductor) transistors. This is done to achieve balanced rise/fall times, as well as to optimize drive strength and power dissipation.

Explanation:

The size of a MOS transistor determines its width and length, which directly affects its electrical characteristics. Here's why the size of PMOS is kept larger than NMOS:

1. Balancing Rise/Fall Times:

In a CMOS circuit, both PMOS and NMOS transistors are used to implement complementary logic functions. When the input signal transitions from low to high (0 to 1), the PMOS transistor should turn off quickly, and the NMOS transistor should turn on quickly. Similarly, when the input signal transitions from high to low (1 to 0), the PMOS transistor should turn on quickly, and the NMOS transistor should turn off quickly.

By making the PMOS transistor larger, its drive strength increases. This means it can provide more current during switching, leading to faster turn-on and turn-off times. On the other hand, the NMOS transistor can be made smaller to achieve a balanced rise/fall time because it has inherently higher mobility and can switch faster compared to PMOS.

2. Drive Strength:

The drive strength of a transistor determines its ability to drive capacitive loads and overcome parasitic resistances. By making the PMOS transistor larger, its drive strength increases, allowing it to drive larger loads efficiently. This is especially important for complementary logic designs where the PMOS transistor is responsible for driving the pull-up network.

3. Power Dissipation:

Power dissipation in CMOS circuits occurs during switching events when both PMOS and NMOS transistors are conducting simultaneously. By making the PMOS transistor larger, its on-resistance (Rds(on)) decreases, resulting in lower power dissipation during the pull-up phase. This helps in reducing overall power consumption in CMOS designs.

Conclusion:

In summary, the size of the PMOS transistor is kept larger than the NMOS transistor in CMOS designs to achieve balanced rise/fall times, improve drive strength, and reduce power dissipation. This helps in optimizing the performance, power consumption, and reliability of CMOS circuits.

In CMOS designs, the size of PMOS (p-channel metal-oxide-semiconductor) transistors is typically kept larger than the size of NMOS (n-channel metal-oxide-semiconductor) transistors. This is done to achieve balanced rise/fall times, as well as to optimize drive strength and power dissipation.

Explanation:

The size of a MOS transistor determines its width and length, which directly affects its electrical characteristics. Here's why the size of PMOS is kept larger than NMOS:

1. Balancing Rise/Fall Times:

In a CMOS circuit, both PMOS and NMOS transistors are used to implement complementary logic functions. When the input signal transitions from low to high (0 to 1), the PMOS transistor should turn off quickly, and the NMOS transistor should turn on quickly. Similarly, when the input signal transitions from high to low (1 to 0), the PMOS transistor should turn on quickly, and the NMOS transistor should turn off quickly.

By making the PMOS transistor larger, its drive strength increases. This means it can provide more current during switching, leading to faster turn-on and turn-off times. On the other hand, the NMOS transistor can be made smaller to achieve a balanced rise/fall time because it has inherently higher mobility and can switch faster compared to PMOS.

2. Drive Strength:

The drive strength of a transistor determines its ability to drive capacitive loads and overcome parasitic resistances. By making the PMOS transistor larger, its drive strength increases, allowing it to drive larger loads efficiently. This is especially important for complementary logic designs where the PMOS transistor is responsible for driving the pull-up network.

3. Power Dissipation:

Power dissipation in CMOS circuits occurs during switching events when both PMOS and NMOS transistors are conducting simultaneously. By making the PMOS transistor larger, its on-resistance (Rds(on)) decreases, resulting in lower power dissipation during the pull-up phase. This helps in reducing overall power consumption in CMOS designs.

Conclusion:

In summary, the size of the PMOS transistor is kept larger than the NMOS transistor in CMOS designs to achieve balanced rise/fall times, improve drive strength, and reduce power dissipation. This helps in optimizing the performance, power consumption, and reliability of CMOS circuits.

|

Explore Courses for Electrical Engineering (EE) exam

|

|

Question Description

In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)To get higher drive strengthb)To reduce power dissipationc)To get balanced rise/fall timed)All of aboveCorrect answer is option 'C'. Can you explain this answer? for Electrical Engineering (EE) 2025 is part of Electrical Engineering (EE) preparation. The Question and answers have been prepared according to the Electrical Engineering (EE) exam syllabus. Information about In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)To get higher drive strengthb)To reduce power dissipationc)To get balanced rise/fall timed)All of aboveCorrect answer is option 'C'. Can you explain this answer? covers all topics & solutions for Electrical Engineering (EE) 2025 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)To get higher drive strengthb)To reduce power dissipationc)To get balanced rise/fall timed)All of aboveCorrect answer is option 'C'. Can you explain this answer?.

In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)To get higher drive strengthb)To reduce power dissipationc)To get balanced rise/fall timed)All of aboveCorrect answer is option 'C'. Can you explain this answer? for Electrical Engineering (EE) 2025 is part of Electrical Engineering (EE) preparation. The Question and answers have been prepared according to the Electrical Engineering (EE) exam syllabus. Information about In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)To get higher drive strengthb)To reduce power dissipationc)To get balanced rise/fall timed)All of aboveCorrect answer is option 'C'. Can you explain this answer? covers all topics & solutions for Electrical Engineering (EE) 2025 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)To get higher drive strengthb)To reduce power dissipationc)To get balanced rise/fall timed)All of aboveCorrect answer is option 'C'. Can you explain this answer?.

Solutions for In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)To get higher drive strengthb)To reduce power dissipationc)To get balanced rise/fall timed)All of aboveCorrect answer is option 'C'. Can you explain this answer? in English & in Hindi are available as part of our courses for Electrical Engineering (EE).

Download more important topics, notes, lectures and mock test series for Electrical Engineering (EE) Exam by signing up for free.

Here you can find the meaning of In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)To get higher drive strengthb)To reduce power dissipationc)To get balanced rise/fall timed)All of aboveCorrect answer is option 'C'. Can you explain this answer? defined & explained in the simplest way possible. Besides giving the explanation of

In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)To get higher drive strengthb)To reduce power dissipationc)To get balanced rise/fall timed)All of aboveCorrect answer is option 'C'. Can you explain this answer?, a detailed solution for In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)To get higher drive strengthb)To reduce power dissipationc)To get balanced rise/fall timed)All of aboveCorrect answer is option 'C'. Can you explain this answer? has been provided alongside types of In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)To get higher drive strengthb)To reduce power dissipationc)To get balanced rise/fall timed)All of aboveCorrect answer is option 'C'. Can you explain this answer? theory, EduRev gives you an

ample number of questions to practice In CMOS designs, why size of PMOS is kept larger than size of NMOS?a)To get higher drive strengthb)To reduce power dissipationc)To get balanced rise/fall timed)All of aboveCorrect answer is option 'C'. Can you explain this answer? tests, examples and also practice Electrical Engineering (EE) tests.

|

Explore Courses for Electrical Engineering (EE) exam

|

|

Signup for Free!

Signup to see your scores go up within 7 days! Learn & Practice with 1000+ FREE Notes, Videos & Tests.