Electrical Engineering (EE) Exam > Electrical Engineering (EE) Questions > When both the inputs of a latch are high, the... Start Learning for Free

When both the inputs of a latch are high, the output is unpredictable. What is this condition called?

- a)Bistable

- b)Indeterminate

- c)Inactive

- d)No change

Correct answer is option 'B'. Can you explain this answer?

Most Upvoted Answer

When both the inputs of a latch are high, the output is unpredictable....

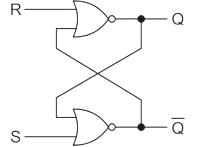

SR Latch:

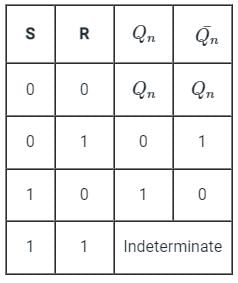

The truth table for SR latch is:

From the above table, when both the inputs of a latch are high, The out is indeterminate.

Free Test

FREE

| Start Free Test |

Community Answer

When both the inputs of a latch are high, the output is unpredictable....

Indeterminate Output Condition in a Latch

Explanation:

When both inputs of a latch are high, meaning that both inputs are at logic level 1, the output of the latch becomes unpredictable. This condition is known as the indeterminate output condition.

Reason for Indeterminate Output:

The indeterminate output condition occurs because both inputs being high causes the latch to enter a metastable state. In this state, the outputs oscillate rapidly between logic 0 and logic 1, resulting in an unpredictable output.

Metastability:

Metastability is a phenomenon that occurs in digital circuits when a flip-flop or latch is in a state of uncertainty or oscillation between logic levels. It can happen when the inputs to the flip-flop or latch change close to the edge of a clock signal. Metastability can cause the output to remain in an unknown state for an indefinite period of time until it eventually stabilizes.

Consequences of Indeterminate Output:

The indeterminate output condition can have several consequences:

1. Data corruption: The unpredictable output can lead to errors in the data being processed or stored by the latch.

2. Timing issues: The indeterminate output can affect the timing of subsequent logic operations, causing timing violations and potential malfunctioning of the circuit.

3. System instability: The unpredictable output can propagate through the system, leading to unstable behavior and unreliable operation.

Preventing Indeterminate Output:

To prevent the indeterminate output condition in a latch, it is important to ensure that both inputs are not simultaneously high. This can be achieved by using proper timing and sequencing of input signals. It is also common practice to use edge-triggered flip-flops instead of latches in critical circuits, as flip-flops have built-in synchronization mechanisms to avoid metastability issues.

Conclusion:

The indeterminate output condition occurs in a latch when both inputs are high, causing the latch to enter a metastable state. This condition can lead to unpredictable outputs, data corruption, timing issues, and system instability. It is important to prevent this condition by carefully designing the timing and sequencing of input signals and considering the use of edge-triggered flip-flops instead of latches in critical circuits.

Explanation:

When both inputs of a latch are high, meaning that both inputs are at logic level 1, the output of the latch becomes unpredictable. This condition is known as the indeterminate output condition.

Reason for Indeterminate Output:

The indeterminate output condition occurs because both inputs being high causes the latch to enter a metastable state. In this state, the outputs oscillate rapidly between logic 0 and logic 1, resulting in an unpredictable output.

Metastability:

Metastability is a phenomenon that occurs in digital circuits when a flip-flop or latch is in a state of uncertainty or oscillation between logic levels. It can happen when the inputs to the flip-flop or latch change close to the edge of a clock signal. Metastability can cause the output to remain in an unknown state for an indefinite period of time until it eventually stabilizes.

Consequences of Indeterminate Output:

The indeterminate output condition can have several consequences:

1. Data corruption: The unpredictable output can lead to errors in the data being processed or stored by the latch.

2. Timing issues: The indeterminate output can affect the timing of subsequent logic operations, causing timing violations and potential malfunctioning of the circuit.

3. System instability: The unpredictable output can propagate through the system, leading to unstable behavior and unreliable operation.

Preventing Indeterminate Output:

To prevent the indeterminate output condition in a latch, it is important to ensure that both inputs are not simultaneously high. This can be achieved by using proper timing and sequencing of input signals. It is also common practice to use edge-triggered flip-flops instead of latches in critical circuits, as flip-flops have built-in synchronization mechanisms to avoid metastability issues.

Conclusion:

The indeterminate output condition occurs in a latch when both inputs are high, causing the latch to enter a metastable state. This condition can lead to unpredictable outputs, data corruption, timing issues, and system instability. It is important to prevent this condition by carefully designing the timing and sequencing of input signals and considering the use of edge-triggered flip-flops instead of latches in critical circuits.

| Explore Courses for Electrical Engineering (EE) exam |  |

Question Description

When both the inputs of a latch are high, the output is unpredictable. What is this condition called?a)Bistableb)Indeterminatec)Inactived)No changeCorrect answer is option 'B'. Can you explain this answer? for Electrical Engineering (EE) 2026 is part of Electrical Engineering (EE) preparation. The Question and answers have been prepared according to the Electrical Engineering (EE) exam syllabus. Information about When both the inputs of a latch are high, the output is unpredictable. What is this condition called?a)Bistableb)Indeterminatec)Inactived)No changeCorrect answer is option 'B'. Can you explain this answer? covers all topics & solutions for Electrical Engineering (EE) 2026 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for When both the inputs of a latch are high, the output is unpredictable. What is this condition called?a)Bistableb)Indeterminatec)Inactived)No changeCorrect answer is option 'B'. Can you explain this answer?.

When both the inputs of a latch are high, the output is unpredictable. What is this condition called?a)Bistableb)Indeterminatec)Inactived)No changeCorrect answer is option 'B'. Can you explain this answer? for Electrical Engineering (EE) 2026 is part of Electrical Engineering (EE) preparation. The Question and answers have been prepared according to the Electrical Engineering (EE) exam syllabus. Information about When both the inputs of a latch are high, the output is unpredictable. What is this condition called?a)Bistableb)Indeterminatec)Inactived)No changeCorrect answer is option 'B'. Can you explain this answer? covers all topics & solutions for Electrical Engineering (EE) 2026 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for When both the inputs of a latch are high, the output is unpredictable. What is this condition called?a)Bistableb)Indeterminatec)Inactived)No changeCorrect answer is option 'B'. Can you explain this answer?.

Solutions for When both the inputs of a latch are high, the output is unpredictable. What is this condition called?a)Bistableb)Indeterminatec)Inactived)No changeCorrect answer is option 'B'. Can you explain this answer? in English & in Hindi are available as part of our courses for Electrical Engineering (EE). Download more important topics, notes, lectures and mock test series for Electrical Engineering (EE) Exam by signing up for free.

Here you can find the meaning of When both the inputs of a latch are high, the output is unpredictable. What is this condition called?a)Bistableb)Indeterminatec)Inactived)No changeCorrect answer is option 'B'. Can you explain this answer? defined & explained in the simplest way possible. Besides giving the explanation of When both the inputs of a latch are high, the output is unpredictable. What is this condition called?a)Bistableb)Indeterminatec)Inactived)No changeCorrect answer is option 'B'. Can you explain this answer?, a detailed solution for When both the inputs of a latch are high, the output is unpredictable. What is this condition called?a)Bistableb)Indeterminatec)Inactived)No changeCorrect answer is option 'B'. Can you explain this answer? has been provided alongside types of When both the inputs of a latch are high, the output is unpredictable. What is this condition called?a)Bistableb)Indeterminatec)Inactived)No changeCorrect answer is option 'B'. Can you explain this answer? theory, EduRev gives you an ample number of questions to practice When both the inputs of a latch are high, the output is unpredictable. What is this condition called?a)Bistableb)Indeterminatec)Inactived)No changeCorrect answer is option 'B'. Can you explain this answer? tests, examples and also practice Electrical Engineering (EE) tests.

| Explore Courses for Electrical Engineering (EE) exam |  |

Top Courses for Electrical Engineering (EE)

Explore CoursesSignup for Free!

Signup to see your scores go up within 7 days! Learn & Practice with 1000+ FREE Notes, Videos & Tests.