All questions of Digital Electronics for Electrical Engineering (EE) Exam

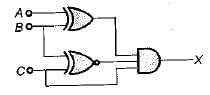

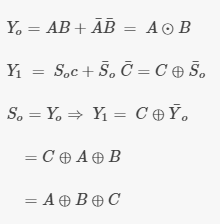

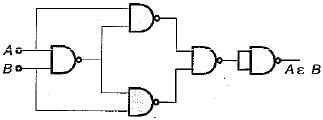

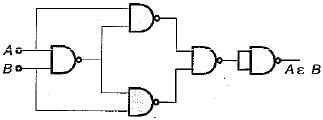

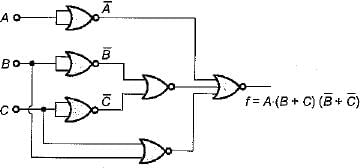

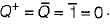

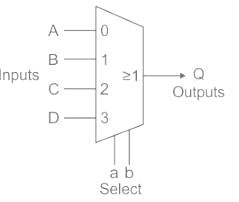

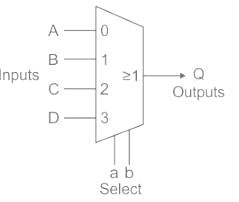

A MUX network is shown in fig. Que: This circuit act as a

Que: This circuit act as a- a)Full adder

- b)Half adder

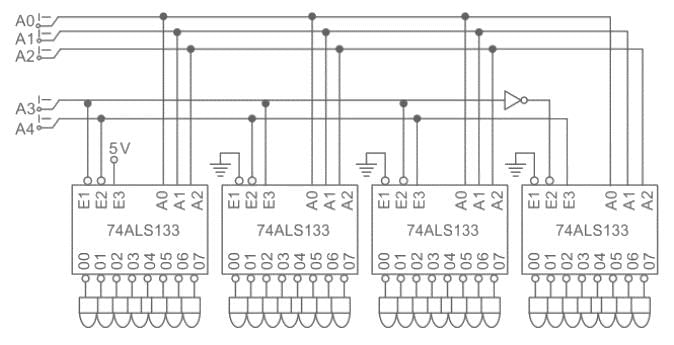

- c)Full subtractor

- d)Half subtractor

Correct answer is option 'A'. Can you explain this answer?

A MUX network is shown in fig.

Que: This circuit act as a

a)

Full adder

b)

Half adder

c)

Full subtractor

d)

Half subtractor

| Naroj Boda answered |

A 64 × 1 multiplexer has 64 inputs so if we use 2 × 1 multiplexers 32 are needed in the first stage for 64 inputs, the output of these 32 multiplexers are connected to inputs of 16 multiplexers in the second stage.

Similarly, in third stage, 8 (2 × 1) multiplexers are used, in fourth stage 4 are used and finally 2 (2 × 1) multiplexers in the fifth stage, 1 in the sixth stage.

Total 2 × 1 multiplexers needed are 32 + 16 + 8 + 4 + 2 + 1 = 63

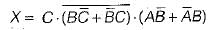

Can you explain the answer of this question below:A switching function of four variable, f (w, x y, z) is to equal the product of two other function f1 and f2, of the same variable f = f1f2 . The function f and f1 are as follows :

f = ∑m(4,7,15)

f = ∑m(0,1,2, 3, 4,7, 8,9,10,11,15)

Que: The number of full specified function, that will satisfy the given condition, is

- A:

32

- B:

16

- C:

4

- D:

1

The answer is a.

A switching function of four variable, f (w, x y, z) is to equal the product of two other function f1 and f2, of the same variable f = f1f2 . The function f and f1 are as follows :

f = ∑m(4,7,15)

f = ∑m(0,1,2, 3, 4,7, 8,9,10,11,15)

Que: The number of full specified function, that will satisfy the given condition, is

32

16

4

1

| | Ravi Singh answered |

f = ∑m(4,7,15)

f1 = ∑m(0,1,2, 3, 4,7, 8,9,10,11,15)

f2 = ∑m(4,7,15) + ∑dc(5, 6, 12, 13, 14)

There are 5 don't care condition. So 25 = 32 different functions f2

11001, 1001 and 111001 correspond to the 2’s complement representation of the following set of numbers- a)25, 9 and 57 respectively

- b)-6, -6 and -6 respectively

- c)-7, -7 and -7 respectively

- d)-25, -9 and -57 respectively

Correct answer is option 'C'. Can you explain this answer?

11001, 1001 and 111001 correspond to the 2’s complement representation of the following set of numbers

a)

25, 9 and 57 respectively

b)

-6, -6 and -6 respectively

c)

-7, -7 and -7 respectively

d)

-25, -9 and -57 respectively

| Swara Dasgupta answered |

2's complement of 11001 = 00110 + 1 = 00111

00111 is 7 in decimal, so 11001 is 2's complement representation of -7.

2's complement of 1001 = 0110 + 1 = 0111

0111 is 7 in decimal, so 1001 is 2's complement representation of -7.

2's complement of 111001 = 000110 + 1 = 000111

000111 is 7 in decimal, so 111001 is 2's complement representation of -7.

The circuits of NOR based S-R latch classified as asynchronous sequential circuits, why?- a)Because of inverted outputs

- b)Because of triggering functionality

- c)Because of cross-coupled connection

- d)Because of inverted outputs & triggering functionality

Correct answer is option 'C'. Can you explain this answer?

The circuits of NOR based S-R latch classified as asynchronous sequential circuits, why?

a)

Because of inverted outputs

b)

Because of triggering functionality

c)

Because of cross-coupled connection

d)

Because of inverted outputs & triggering functionality

| Advait Verma answered |

Introduction to NOR-Based S-R Latch

A NOR-based Set-Reset (S-R) latch is a fundamental building block in digital electronics, classified as an asynchronous sequential circuit. The classification stems from its inherent characteristics and operational mechanisms.

Understanding Asynchronous Sequential Circuits

- Definition: Asynchronous sequential circuits are those that do not rely on a clock signal for state changes. Instead, they change states based on input signals directly.

- Key Feature: The output of such circuits can change immediately in response to changes in input, making them asynchronous.

Why Cross-Coupled Connections Matter

- Cross-Coupled Configuration: The S-R latch utilizes feedback through cross-coupled NOR gates. This configuration enables the circuit to maintain its state until a new input is applied.

- State Retention: When one of the inputs (Set or Reset) is activated, it alters the state of the output. The feedback loop maintains this state even after the input is removed, underscoring the asynchronous nature.

Other Considerations

- Inverted Outputs: Although the outputs of a NOR gate are inverted, this alone does not classify the latch as asynchronous.

- Triggering Functionality: While triggering is relevant, it is not the primary reason for labeling the latch as asynchronous.

Conclusion

In summary, the cross-coupled connections in a NOR-based S-R latch are the primary reason for its classification as an asynchronous sequential circuit. The feedback mechanism allows the latch to change states based solely on input changes, independent of a clock signal.

A NOR-based Set-Reset (S-R) latch is a fundamental building block in digital electronics, classified as an asynchronous sequential circuit. The classification stems from its inherent characteristics and operational mechanisms.

Understanding Asynchronous Sequential Circuits

- Definition: Asynchronous sequential circuits are those that do not rely on a clock signal for state changes. Instead, they change states based on input signals directly.

- Key Feature: The output of such circuits can change immediately in response to changes in input, making them asynchronous.

Why Cross-Coupled Connections Matter

- Cross-Coupled Configuration: The S-R latch utilizes feedback through cross-coupled NOR gates. This configuration enables the circuit to maintain its state until a new input is applied.

- State Retention: When one of the inputs (Set or Reset) is activated, it alters the state of the output. The feedback loop maintains this state even after the input is removed, underscoring the asynchronous nature.

Other Considerations

- Inverted Outputs: Although the outputs of a NOR gate are inverted, this alone does not classify the latch as asynchronous.

- Triggering Functionality: While triggering is relevant, it is not the primary reason for labeling the latch as asynchronous.

Conclusion

In summary, the cross-coupled connections in a NOR-based S-R latch are the primary reason for its classification as an asynchronous sequential circuit. The feedback mechanism allows the latch to change states based solely on input changes, independent of a clock signal.

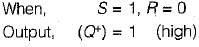

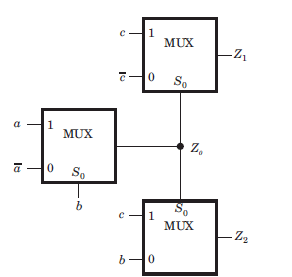

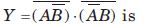

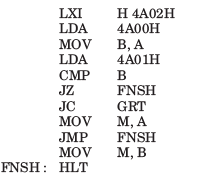

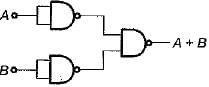

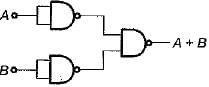

The reduced form of the Boolean expression of

- a)A + B

- b)

- c)

- d)

Correct answer is option 'C'. Can you explain this answer?

The reduced form of the Boolean expression of

a)

A + B

b)

c)

d)

| | Arya Tiwari answered |

On multiplying the decimal number continuously by 2, the binary equivalent is obtained.

Each product term of a group, w’.x.y’ and w.y, represents the ____________ in that group.- a)Input

- b)POS

- c)Sum-of-Minterms

- d)Sum of Maxterms

Correct answer is option 'C'. Can you explain this answer?

Each product term of a group, w’.x.y’ and w.y, represents the ____________ in that group.

a)

Input

b)

POS

c)

Sum-of-Minterms

d)

Sum of Maxterms

| | Rounak Rane answered |

Ith n variables, is a combination of these variables raised to powers of 0 or 1.

A signed integer has been stored in a byte using 2’s complement format. We wish to store the same integer in 16-bit word. We should copy the original byte to the less significant byte of the word and fill the more significant byte with- a)0

- b)1

- c)equal to the MSB of the original byte

- d)complement of the MSB of the original byte.

Correct answer is option 'C'. Can you explain this answer?

A signed integer has been stored in a byte using 2’s complement format. We wish to store the same integer in 16-bit word. We should copy the original byte to the less significant byte of the word and fill the more significant byte with

a)

0

b)

1

c)

equal to the MSB of the original byte

d)

complement of the MSB of the original byte.

| Navya Sarkar answered |

See a example

A switching function of four variable, f (w, x y, ... morez) is to equal the product of two other function f1and f2, of the same variable f = f1f2.The function f and f1are as follows : f =∑m(4,7,15) , f1 =∑m(0,1,2, 3, 4,7, 8,9,10,11,15)Que: The simplest function for f2 isa) xb)  c) yd)

c) yd)  Correct answer is option 'A'. Can you explain this answer?

Correct answer is option 'A'. Can you explain this answer?

| Aim It Academy answered |

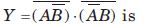

Consider the following set of instruction If BYTE1 = 07H, then content of A, after the execution of program will be

If BYTE1 = 07H, then content of A, after the execution of program will be- a)46H

- b)70H

- c)38H

- d)68H

Correct answer is option 'A'. Can you explain this answer?

Consider the following set of instruction

If BYTE1 = 07H, then content of A, after the execution of program will be

a)

46H

b)

70H

c)

38H

d)

68H

| | Sanvi Kapoor answered |

This program multiply BYTE1 by 10. Hence content of A will be 46H.

07H = 0710 , 7 x 10 = 70, 7010 = 46H

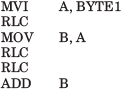

Consider the following statements associated with logic gates:

1. Logic circuit of any complexity can be realised by using only the three basic gates namely AND, GR and NOT.

2. AND, OR and NOT .gates are called universal building blocks.

3. AND/OR/INVERT logic (AO! logic) can be converted to NAND logic or NOR logic.

4. A NAND gate can be used as an inverter by connecting all its input terminals except one, to logic 1 and applying the signal to be inverted to the remaining terminal.

Q. Which of the statements given above is/are correct?- a)1,3 and 4

- b)Only 3

- c)1 and 3

- d)1 and 4

Correct answer is option 'C'. Can you explain this answer?

Consider the following statements associated with logic gates:

1. Logic circuit of any complexity can be realised by using only the three basic gates namely AND, GR and NOT.

2. AND, OR and NOT .gates are called universal building blocks.

3. AND/OR/INVERT logic (AO! logic) can be converted to NAND logic or NOR logic.

4. A NAND gate can be used as an inverter by connecting all its input terminals except one, to logic 1 and applying the signal to be inverted to the remaining terminal.

Q. Which of the statements given above is/are correct?

1. Logic circuit of any complexity can be realised by using only the three basic gates namely AND, GR and NOT.

2. AND, OR and NOT .gates are called universal building blocks.

3. AND/OR/INVERT logic (AO! logic) can be converted to NAND logic or NOR logic.

4. A NAND gate can be used as an inverter by connecting all its input terminals except one, to logic 1 and applying the signal to be inverted to the remaining terminal.

Q. Which of the statements given above is/are correct?

a)

1,3 and 4

b)

Only 3

c)

1 and 3

d)

1 and 4

| | Dhruv Datta answered |

- Statement-1 is correct because any circuit can be realized using AND, OR and NOT gates.

- The two logic gates NAND and NOR can realize any logic circuit single-handedly. Hence, these two gates are called universal building blocks. AND, OR and NOT are called basic gates. Thus, statement-2 is not correct.

- Both NAND and NOR gates can perform all the three basic logic functions (AND, OR and NOT). Therefore, AND/OR/INVERT logic can be converted to NAND logic or NOR logic. Hence, statement-3 is correct.

Statement-4 is not correct.

The output Y of a 2-bit comparator is logic 1 whenever the 2-bit input A is greater than the 2-bit input B. The number of combinations for which the output is logic 1, is- a)4

- b)6

- c)8

- d)10

Correct answer is option 'B'. Can you explain this answer?

The output Y of a 2-bit comparator is logic 1 whenever the 2-bit input A is greater than the 2-bit input B. The number of combinations for which the output is logic 1, is

a)

4

b)

6

c)

8

d)

10

| Cstoppers Instructors answered |

The only possible combinations are

A = 01 and B = 0 0

A = 10 and B = 00, 01

A = 11 and B = 00, 01, 10

So there are only 6 combinations

Tips and Tricks:

where n = 2 bit

A = 01 and B = 0 0

A = 10 and B = 00, 01

A = 11 and B = 00, 01, 10

So there are only 6 combinations

Tips and Tricks:

where n = 2 bit

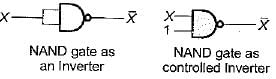

Consider the following program of 8085 assembly language: Que: The memory requirement for this program is

Que: The memory requirement for this program is- a)20 Byte

- b)21 Byte

- c)23 Byte

- d)18 Byte

Correct answer is option 'C'. Can you explain this answer?

Consider the following program of 8085 assembly language:

Que: The memory requirement for this program is

a)

20 Byte

b)

21 Byte

c)

23 Byte

d)

18 Byte

| | Kabir Verma answered |

Operand R, M or implied : 1–Byte instruction

Operand 8–bit : 2–Byte instruction

Operand 16–bit : 3–Byte instruction

Operand 8–bit : 2–Byte instruction

Operand 16–bit : 3–Byte instruction

3–Byte instruction are: LXI, LDA, JZ, JC, JMP

P–Byte instruction are : MOV, CMP, HLT

P–Byte instruction are : MOV, CMP, HLT

Hence memory = 3 x 6 + 1 x 5 = 23 bytes

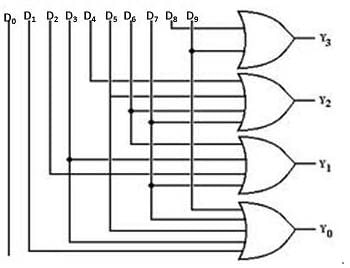

How many OR gates are required for a Decimal-to-bcd encoder?- a)2

- b)10

- c)3

- d)4

Correct answer is option 'D'. Can you explain this answer?

How many OR gates are required for a Decimal-to-bcd encoder?

a)

2

b)

10

c)

3

d)

4

| | Pooja Patel answered |

An encoder is a combinational circuit encoding the information of 2n input lines to n output lines, thus producing the binary equivalent of the input.

This is clear from the diagram that it requires 4 OR gates:

This is clear from the diagram that it requires 4 OR gates:

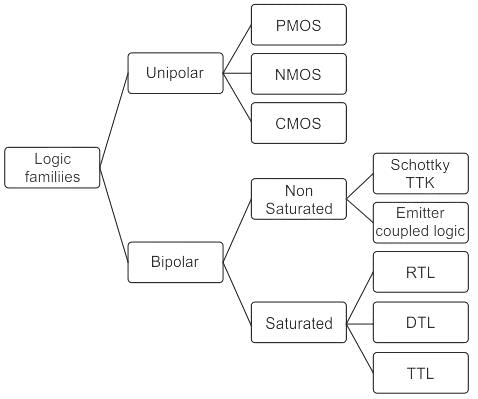

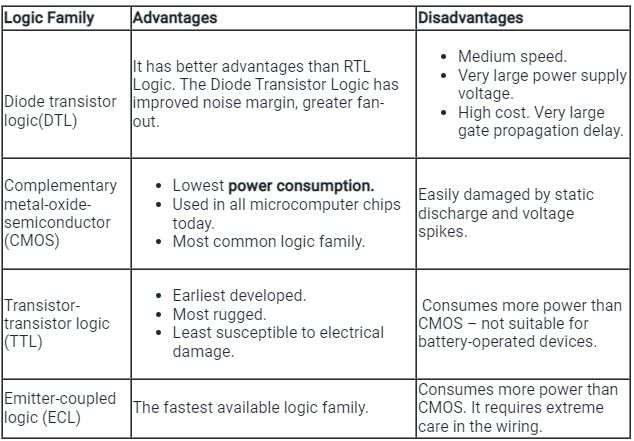

Which logic family dissipates the minimum power?- a)DTL

- b)TTL

- c)ECL

- d)CMOS

Correct answer is option 'D'. Can you explain this answer?

Which logic family dissipates the minimum power?

a)

DTL

b)

TTL

c)

ECL

d)

CMOS

| Cstoppers Instructors answered |

A logic family is one of two related concepts: A logic family of monolithic digital integrated circuit devices is a group of electronic logic gates constructed using one of several different designs, usually with compatible logic levels and power supply characteristics within a family.

What is the function of an enable input on a multiplexer chip?- a)To apply Vcc

- b)To connect ground

- c)To active the entire chip

- d)To active one half of the chip

Correct answer is option 'C'. Can you explain this answer?

What is the function of an enable input on a multiplexer chip?

a)

To apply Vcc

b)

To connect ground

c)

To active the entire chip

d)

To active one half of the chip

| | Siddharth Khanna answered |

The function of an enable input on a multiplexer chip is to activate or deactivate the entire chip. When the enable input is high (or active), the multiplexer chip is enabled and can perform its intended function. On the other hand, when the enable input is low (or inactive), the multiplexer chip is disabled and its outputs are in a high-impedance state.

When the enable input is active, the multiplexer chip acts as a data selector, allowing one of multiple inputs to be selected and routed to the output. The selection of the input is determined by the control inputs of the chip.

Below is a detailed explanation of the function of the enable input on a multiplexer chip:

1. Multiplexer Basics:

- A multiplexer, also known as a data selector, is a digital circuit that selects one of many inputs and routes it to a single output.

- It is commonly represented by the symbol ⊕ or MUX.

2. Enable Input:

- The enable input on a multiplexer chip is denoted as EN or E, and it controls the activation of the chip.

- The enable input is typically an active-high input, meaning that when it is high (logic 1), the chip is enabled.

3. Chip Activation:

- When the enable input is active (high), the multiplexer chip is enabled and can perform its function.

- The chip becomes operational, and its outputs are determined by the control inputs and the selected input.

- The selected input is determined by the control inputs, such as address lines or select inputs.

4. Chip Deactivation:

- When the enable input is inactive (low), the multiplexer chip is disabled.

- The chip enters a high-impedance state, which means that its outputs are effectively disconnected and do not drive any signal.

- This high-impedance state prevents any interference or conflicts with other circuitry that may be connected to the outputs of the disabled chip.

5. Usefulness of Enable Input:

- The enable input is useful in applications where the activation or deactivation of the multiplexer chip needs to be controlled.

- It allows for greater flexibility in circuit design by providing the ability to enable or disable the chip as needed.

In summary, the enable input on a multiplexer chip is responsible for activating or deactivating the entire chip. When the enable input is high, the chip is enabled and can perform its function of selecting and routing one of multiple inputs to the output. When the enable input is low, the chip is disabled, and its outputs are in a high-impedance state.

When the enable input is active, the multiplexer chip acts as a data selector, allowing one of multiple inputs to be selected and routed to the output. The selection of the input is determined by the control inputs of the chip.

Below is a detailed explanation of the function of the enable input on a multiplexer chip:

1. Multiplexer Basics:

- A multiplexer, also known as a data selector, is a digital circuit that selects one of many inputs and routes it to a single output.

- It is commonly represented by the symbol ⊕ or MUX.

2. Enable Input:

- The enable input on a multiplexer chip is denoted as EN or E, and it controls the activation of the chip.

- The enable input is typically an active-high input, meaning that when it is high (logic 1), the chip is enabled.

3. Chip Activation:

- When the enable input is active (high), the multiplexer chip is enabled and can perform its function.

- The chip becomes operational, and its outputs are determined by the control inputs and the selected input.

- The selected input is determined by the control inputs, such as address lines or select inputs.

4. Chip Deactivation:

- When the enable input is inactive (low), the multiplexer chip is disabled.

- The chip enters a high-impedance state, which means that its outputs are effectively disconnected and do not drive any signal.

- This high-impedance state prevents any interference or conflicts with other circuitry that may be connected to the outputs of the disabled chip.

5. Usefulness of Enable Input:

- The enable input is useful in applications where the activation or deactivation of the multiplexer chip needs to be controlled.

- It allows for greater flexibility in circuit design by providing the ability to enable or disable the chip as needed.

In summary, the enable input on a multiplexer chip is responsible for activating or deactivating the entire chip. When the enable input is high, the chip is enabled and can perform its function of selecting and routing one of multiple inputs to the output. When the enable input is low, the chip is disabled, and its outputs are in a high-impedance state.

It is possible for an enable or strobe input to undergo an expansion of two or more MUX ICs to the digital multiplexer with the proficiency of large number of _______- a)Inputs

- b)Outputs

- c)Selection lines

- d)Enable lines

Correct answer is option 'A'. Can you explain this answer?

It is possible for an enable or strobe input to undergo an expansion of two or more MUX ICs to the digital multiplexer with the proficiency of large number of _______

a)

Inputs

b)

Outputs

c)

Selection lines

d)

Enable lines

| | Ashutosh Majumdar answered |

Answer:

To understand the answer to this question, let's first discuss the basic concept of a digital multiplexer.

A digital multiplexer, also known as a data selector, is a combinational circuit that selects one of many input signals and routes it to a single output line based on the control inputs. It is widely used in various electronic applications, such as data transmission, signal routing, and digital communication systems.

A multiplexer can have multiple inputs, outputs, and selection lines. The selection lines determine which input signal gets routed to the output line. The number of selection lines in a multiplexer is determined by the number of input lines and is given by the equation:

n = log2(N)

Where n is the number of selection lines and N is the number of input lines. For example, if we have 4 input lines, we would need 2 selection lines (n = log2(4) = 2).

In the given question, it is mentioned that an enable or strobe input undergoes an expansion of two or more multiplexer ICs. This means that multiple multiplexer ICs are cascaded together to form a larger multiplexer.

When multiple multiplexer ICs are cascaded, the enable or strobe input of each IC is connected in parallel. This allows the enable or strobe input to control the operation of all the cascaded ICs simultaneously.

By expanding the multiplexer using multiple ICs, we can increase the number of inputs that can be selected. Each IC will have a certain number of inputs, outputs, and selection lines. By cascading multiple ICs together, we can effectively increase the number of inputs of the multiplexer.

However, it is important to note that the number of outputs and selection lines remains the same, as these are determined by the individual ICs. Only the number of inputs can be increased by cascading multiple ICs.

Therefore, the correct answer to the given question is option 'A' - Inputs.

To understand the answer to this question, let's first discuss the basic concept of a digital multiplexer.

A digital multiplexer, also known as a data selector, is a combinational circuit that selects one of many input signals and routes it to a single output line based on the control inputs. It is widely used in various electronic applications, such as data transmission, signal routing, and digital communication systems.

A multiplexer can have multiple inputs, outputs, and selection lines. The selection lines determine which input signal gets routed to the output line. The number of selection lines in a multiplexer is determined by the number of input lines and is given by the equation:

n = log2(N)

Where n is the number of selection lines and N is the number of input lines. For example, if we have 4 input lines, we would need 2 selection lines (n = log2(4) = 2).

In the given question, it is mentioned that an enable or strobe input undergoes an expansion of two or more multiplexer ICs. This means that multiple multiplexer ICs are cascaded together to form a larger multiplexer.

When multiple multiplexer ICs are cascaded, the enable or strobe input of each IC is connected in parallel. This allows the enable or strobe input to control the operation of all the cascaded ICs simultaneously.

By expanding the multiplexer using multiple ICs, we can increase the number of inputs that can be selected. Each IC will have a certain number of inputs, outputs, and selection lines. By cascading multiple ICs together, we can effectively increase the number of inputs of the multiplexer.

However, it is important to note that the number of outputs and selection lines remains the same, as these are determined by the individual ICs. Only the number of inputs can be increased by cascading multiple ICs.

Therefore, the correct answer to the given question is option 'A' - Inputs.

If half adders and full adders are implements using gates, then for the addition of two 17 bit numbers (using minimum gates) the number of half adders and full adders required will be- a)0, 17

- b)16, 1

- c)1, 16

- d)8, 8

Correct answer is option 'C'. Can you explain this answer?

If half adders and full adders are implements using gates, then for the addition of two 17 bit numbers (using minimum gates) the number of half adders and full adders required will be

a)

0, 17

b)

16, 1

c)

1, 16

d)

8, 8

| | Xara Das answered |

Understanding Half Adders and Full Adders

In digital electronics, half adders and full adders are crucial components for performing binary addition.

- Half Adder: Takes two single-bit inputs and produces a sum and a carry output. It cannot handle carry input.

- Full Adder: Takes three inputs (two significant bits and an incoming carry) and produces a sum and a carry output. It can handle carry input from a previous stage.

Adding Two 17-Bit Numbers

When adding two 17-bit binary numbers, consider how half adders and full adders fit into the process:

1. Most Significant Bit (MSB):

- The addition starts from the least significant bit (LSB) and moves toward the MSB.

- For the first bit (LSB), a half adder is used because there are no carry-ins from previous bits.

2. Subsequent Bits:

- For the next 16 bits, full adders are used. Each full adder takes the sum of the previous bits and the carry from the previous step.

Counting the Adders

- Half Adders:

- Only 1 half adder is needed for the LSB.

- Full Adders:

- 16 full adders are needed for the remaining 16 bits.

Conclusion

Thus, the number of adders required for adding two 17-bit numbers efficiently is:

- Half Adders: 1

- Full Adders: 16

This leads to the correct answer being option C: 1, 16. The configuration uses the minimum number of gates for the addition process.

In digital electronics, half adders and full adders are crucial components for performing binary addition.

- Half Adder: Takes two single-bit inputs and produces a sum and a carry output. It cannot handle carry input.

- Full Adder: Takes three inputs (two significant bits and an incoming carry) and produces a sum and a carry output. It can handle carry input from a previous stage.

Adding Two 17-Bit Numbers

When adding two 17-bit binary numbers, consider how half adders and full adders fit into the process:

1. Most Significant Bit (MSB):

- The addition starts from the least significant bit (LSB) and moves toward the MSB.

- For the first bit (LSB), a half adder is used because there are no carry-ins from previous bits.

2. Subsequent Bits:

- For the next 16 bits, full adders are used. Each full adder takes the sum of the previous bits and the carry from the previous step.

Counting the Adders

- Half Adders:

- Only 1 half adder is needed for the LSB.

- Full Adders:

- 16 full adders are needed for the remaining 16 bits.

Conclusion

Thus, the number of adders required for adding two 17-bit numbers efficiently is:

- Half Adders: 1

- Full Adders: 16

This leads to the correct answer being option C: 1, 16. The configuration uses the minimum number of gates for the addition process.

The number of two input NAND gate required to implement an OR gate and an EX-NOR gate are respectively- a)2 and 5

- b)3 and 4

- c)3 and 5

- d)2 and 4

Correct answer is option 'C'. Can you explain this answer?

The number of two input NAND gate required to implement an OR gate and an EX-NOR gate are respectively

a)

2 and 5

b)

3 and 4

c)

3 and 5

d)

2 and 4

| | Prasad Saini answered |

OR gate using NAND gate:

EX-NOR gate using NAND gate:

Thus, we require 3 NAND gates for an OR gate while 5 NAND gates for an EX-NOR gate.

EX-NOR gate using NAND gate:

Thus, we require 3 NAND gates for an OR gate while 5 NAND gates for an EX-NOR gate.

Consider the following statements associated with the use of various adder circuits:

1. A ripple carry adder is a parallel adder in which the carry-out of each full-adder is the carry-in to the next most significant adder.

2. Serial adders are used where speed is more important than circuit minimization.

3. The look-ahead carry adder speeds up the process by eliminating the ripple carry.

4. Serial adders are faster than parallel addersWhich of the statements given above are correct?- a)1,2 and 4

- b)2 and 4 only

- c)1 and 3 only

- d)2, 3 and 4

Correct answer is option 'C'. Can you explain this answer?

Consider the following statements associated with the use of various adder circuits:

1. A ripple carry adder is a parallel adder in which the carry-out of each full-adder is the carry-in to the next most significant adder.

2. Serial adders are used where speed is more important than circuit minimization.

3. The look-ahead carry adder speeds up the process by eliminating the ripple carry.

4. Serial adders are faster than parallel adders

1. A ripple carry adder is a parallel adder in which the carry-out of each full-adder is the carry-in to the next most significant adder.

2. Serial adders are used where speed is more important than circuit minimization.

3. The look-ahead carry adder speeds up the process by eliminating the ripple carry.

4. Serial adders are faster than parallel adders

Which of the statements given above are correct?

a)

1,2 and 4

b)

2 and 4 only

c)

1 and 3 only

d)

2, 3 and 4

| | Sanchita Choudhary answered |

- Serial adders are used where circuit minimization is more important than speed because they require one clock pulse for each pair of bits added and hence slower than parallel adders. Thus, statements 2 and 4 are not correct.

- Statements 1 and 3 are correct.

Consider the following statements:

1. Sequential circuits are always faster than combination circuits.

2. In an asynchronous circuit there is no problem of stability.

3. The logic circuits whose outputs at any instant of time depend only on the input signals present at that time are known as combinational circuits.

4. In a combinational circuit, for a change in the input, the output appears immediately.

5. In a sequential circuits, the output signals are fed back to the input side.Which of the statement given above are correct? - a)2, 3 and 4

- b)1. and 5 only

- c)3 and 5 only

- d)1,2 and 4

Correct answer is option 'C'. Can you explain this answer?

Consider the following statements:

1. Sequential circuits are always faster than combination circuits.

2. In an asynchronous circuit there is no problem of stability.

3. The logic circuits whose outputs at any instant of time depend only on the input signals present at that time are known as combinational circuits.

4. In a combinational circuit, for a change in the input, the output appears immediately.

5. In a sequential circuits, the output signals are fed back to the input side.

1. Sequential circuits are always faster than combination circuits.

2. In an asynchronous circuit there is no problem of stability.

3. The logic circuits whose outputs at any instant of time depend only on the input signals present at that time are known as combinational circuits.

4. In a combinational circuit, for a change in the input, the output appears immediately.

5. In a sequential circuits, the output signals are fed back to the input side.

Which of the statement given above are correct?

a)

2, 3 and 4

b)

1. and 5 only

c)

3 and 5 only

d)

1,2 and 4

| | Muskaan Nair answered |

• Combinational circuits are often faster than sequential circuits since the combinations circuits do not require memory whereas the sequential circuits need memory devices to perform their operations in sequence. Hence statement - 1 is not correct.

• in an asynchronous circuit, events are allowed to occur without any synchronisation In such a case, the system become: unstable which results in difficulties. Hence statement-2 is not correct.

• Statement-3 is correct which is the definitioi of a combinational circuit.

• in a combinational circuit, for a change if the input, the output appears immediately except for the propagation delay througt circuit gates. Thus, statement-4 is no correct.

• In a sequential circuit, an output signal is e function of the present input signals and e sequence of the past input signals i.e. the past output signals since the output signals are fed back to the input side. Hence, statement-5 is correct.

Thus, statements 3 and 5 are only correct.

• in an asynchronous circuit, events are allowed to occur without any synchronisation In such a case, the system become: unstable which results in difficulties. Hence statement-2 is not correct.

• Statement-3 is correct which is the definitioi of a combinational circuit.

• in a combinational circuit, for a change if the input, the output appears immediately except for the propagation delay througt circuit gates. Thus, statement-4 is no correct.

• In a sequential circuit, an output signal is e function of the present input signals and e sequence of the past input signals i.e. the past output signals since the output signals are fed back to the input side. Hence, statement-5 is correct.

Thus, statements 3 and 5 are only correct.

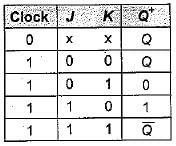

What J-K input condition will always set ‘Q+ upon the occurrence of the active clock transition ?- a)J = 1, K = 0

- b)J = 1 , K = 1

- c)J = 0 , K = 1

- d)J = 0, K = 0

Correct answer is option 'A'. Can you explain this answer?

What J-K input condition will always set ‘Q+ upon the occurrence of the active clock transition ?

a)

J = 1, K = 0

b)

J = 1 , K = 1

c)

J = 0 , K = 1

d)

J = 0, K = 0

| | Shivam Das answered |

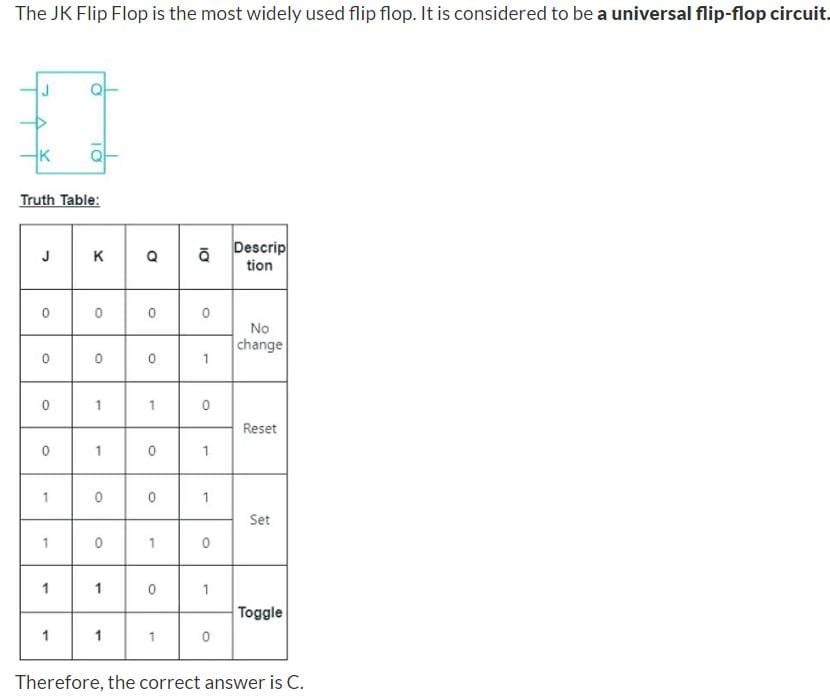

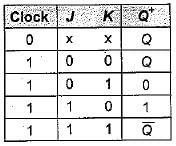

Truth table for J-K flip-flop is shown below.

When J = 1 and K = 0, output (Q+) is always set upon the occurrence of the active clock transition.

When J = 1 and K = 0, output (Q+) is always set upon the occurrence of the active clock transition.

Synchronous counter is a type of ____________- a)SSI counters

- b)LSI counters

- c)MSI counters

- d)VLSI counters

Correct answer is option 'C'. Can you explain this answer?

Synchronous counter is a type of ____________

a)

SSI counters

b)

LSI counters

c)

MSI counters

d)

VLSI counters

| | Pooja Patel answered |

Synchronous Counter is a Medium Scale Integrated (MSI). In Synchronous Counters, the clock pulse is supplied to all the flip-flops simultaneously.

In the truth table of an N-input OR gate, in the column for the output of the gate,- a)the number of zeros is equal to N.

- b)the number of zeros is always 1.

- c)the output is zero if any one of the input is zero

- d)the number of times a zero occurs is a complex function of N.

Correct answer is option 'B'. Can you explain this answer?

In the truth table of an N-input OR gate, in the column for the output of the gate,

a)

the number of zeros is equal to N.

b)

the number of zeros is always 1.

c)

the output is zero if any one of the input is zero

d)

the number of times a zero occurs is a complex function of N.

| | Vaibhav Joshi answered |

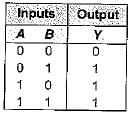

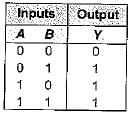

A two input OR gate truth table is shown below:

From the truth table of OR gate it is clear tha output is 0’s only when all the inputs are 0’s otherwise for all other input combination outpu is always 1's. Hence, in the column for the outpu of the OR gate, the number of zeros is always 1's.

From the truth table of OR gate it is clear tha output is 0’s only when all the inputs are 0’s otherwise for all other input combination outpu is always 1's. Hence, in the column for the outpu of the OR gate, the number of zeros is always 1's.

Find the number of 2 × 1 MUX (multiplexers) required to implement 16 × 1 MUX.- a)15

- b)20

- c)5

- d)9

Correct answer is option 'A'. Can you explain this answer?

Find the number of 2 × 1 MUX (multiplexers) required to implement 16 × 1 MUX.

a)

15

b)

20

c)

5

d)

9

| | Mayank Sengupta answered |

It seems like you were cut off mid-sentence. Could you please provide more context or complete your question?

Which is the major functioning responsibility of the multiplexing combinational circuit?- a)Decoding the binary information

- b)Generation of all minterms in an output function with OR-gate

- c)Generation of selected path between multiple sources and a single destination

- d)Encoding of binary information

Correct answer is option 'C'. Can you explain this answer?

Which is the major functioning responsibility of the multiplexing combinational circuit?

a)

Decoding the binary information

b)

Generation of all minterms in an output function with OR-gate

c)

Generation of selected path between multiple sources and a single destination

d)

Encoding of binary information

| Isha Bajaj answered |

The major functioning responsibility of a multiplexing combinational circuit is the generation of a selected path between multiple sources and a single destination. Let's break down this answer in detail:

1. What is a multiplexing combinational circuit?

A multiplexing combinational circuit is a digital circuit that allows multiple input signals to be transmitted over a single transmission line or channel. It uses a combination of logic gates to select and route the desired input signal to the output.

2. Understanding the options:

a) Decoding the binary information:

Decoding refers to the process of converting a binary code into a more meaningful form. While decoding can be a part of the multiplexing process, it is not the major functioning responsibility of the circuit.

b) Generation of all minterms in an output function with OR-gate:

A minterm is a product term in Boolean algebra that represents a specific combination of input variables. While generating minterms can be a part of the multiplexing process, it is not the major functioning responsibility of the circuit.

c) Generation of selected path between multiple sources and a single destination:

This is the correct answer. The main purpose of a multiplexing combinational circuit is to select and route the desired input signal to a single output destination. It allows multiple sources to share a common transmission line or channel, enabling efficient communication.

d) Encoding of binary information:

Encoding refers to the process of converting meaningful data into a coded form. While encoding can be a part of the multiplexing process, it is not the major functioning responsibility of the circuit.

3. Importance of selecting a path:

In many applications, especially in communication systems, there is a need to transmit multiple signals over limited resources. Multiplexing allows efficient utilization of these resources by selecting and routing the desired signals to their respective destinations. By choosing the appropriate path, the multiplexing combinational circuit ensures that the desired signal reaches the destination without interference or loss.

4. How the circuit works:

The multiplexing combinational circuit uses logic gates, such as AND gates and OR gates, to select the desired input signal based on control signals. These control signals determine which input signal is routed to the output. By manipulating the control signals, different input signals can be selected and transmitted at different times, effectively sharing the transmission line or channel.

In conclusion, the major functioning responsibility of a multiplexing combinational circuit is to generate a selected path between multiple sources and a single destination. It allows efficient utilization of resources and enables the transmission of multiple signals over a common transmission line or channel.

1. What is a multiplexing combinational circuit?

A multiplexing combinational circuit is a digital circuit that allows multiple input signals to be transmitted over a single transmission line or channel. It uses a combination of logic gates to select and route the desired input signal to the output.

2. Understanding the options:

a) Decoding the binary information:

Decoding refers to the process of converting a binary code into a more meaningful form. While decoding can be a part of the multiplexing process, it is not the major functioning responsibility of the circuit.

b) Generation of all minterms in an output function with OR-gate:

A minterm is a product term in Boolean algebra that represents a specific combination of input variables. While generating minterms can be a part of the multiplexing process, it is not the major functioning responsibility of the circuit.

c) Generation of selected path between multiple sources and a single destination:

This is the correct answer. The main purpose of a multiplexing combinational circuit is to select and route the desired input signal to a single output destination. It allows multiple sources to share a common transmission line or channel, enabling efficient communication.

d) Encoding of binary information:

Encoding refers to the process of converting meaningful data into a coded form. While encoding can be a part of the multiplexing process, it is not the major functioning responsibility of the circuit.

3. Importance of selecting a path:

In many applications, especially in communication systems, there is a need to transmit multiple signals over limited resources. Multiplexing allows efficient utilization of these resources by selecting and routing the desired signals to their respective destinations. By choosing the appropriate path, the multiplexing combinational circuit ensures that the desired signal reaches the destination without interference or loss.

4. How the circuit works:

The multiplexing combinational circuit uses logic gates, such as AND gates and OR gates, to select the desired input signal based on control signals. These control signals determine which input signal is routed to the output. By manipulating the control signals, different input signals can be selected and transmitted at different times, effectively sharing the transmission line or channel.

In conclusion, the major functioning responsibility of a multiplexing combinational circuit is to generate a selected path between multiple sources and a single destination. It allows efficient utilization of resources and enables the transmission of multiple signals over a common transmission line or channel.

The minimum number of NOR gates requires to implement the expression

f(A, B, C) = πM(0, 1, 2, 3, 4, 7) is- a)5

- b)4

- c)7

- d)6

Correct answer is option 'D'. Can you explain this answer?

The minimum number of NOR gates requires to implement the expression

f(A, B, C) = πM(0, 1, 2, 3, 4, 7) is

f(A, B, C) = πM(0, 1, 2, 3, 4, 7) is

a)

5

b)

4

c)

7

d)

6

| | Shivam Das answered |

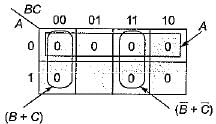

Given expressio n is f = πM( 0, 1, 2, 3, 4, 7)

The K-map for this expression is shown below.

The minimized expression in POS form is

The minimized expression 'f' can be implemented using two input NOR gate as shown below.

Thus, we require six NOR gates.

The K-map for this expression is shown below.

The minimized expression in POS form is

The minimized expression 'f' can be implemented using two input NOR gate as shown below.

Thus, we require six NOR gates.

The flag bits in an ALU is defined as ___________- a)The total number of registers

- b)The status bit conditions

- c)The total number of control lines

- d)All of the Mentioned

Correct answer is option 'B'. Can you explain this answer?

The flag bits in an ALU is defined as ___________

a)

The total number of registers

b)

The status bit conditions

c)

The total number of control lines

d)

All of the Mentioned

| | Pooja Patel answered |

In an ALU, status bit conditions are sometimes called condition code bits or flag bits. It is so called because they tend to represent the status of the respect flags after any operation.

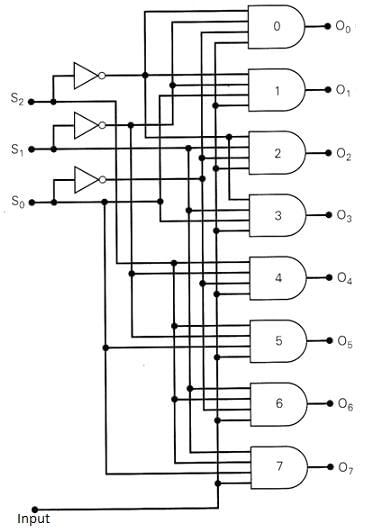

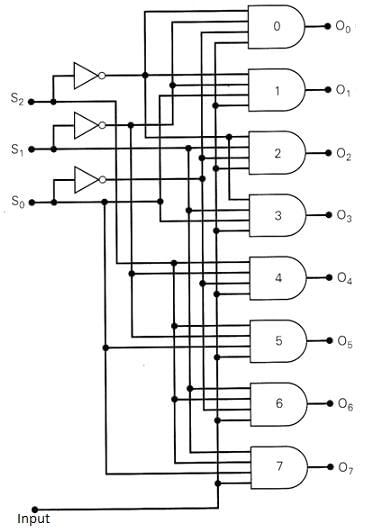

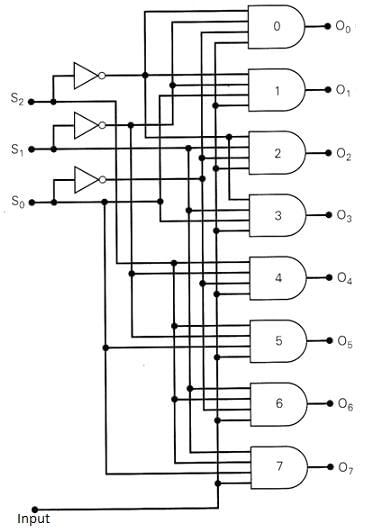

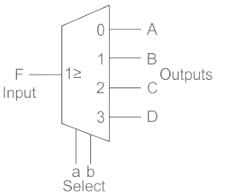

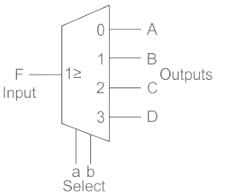

The output Q4 of this 1-to-8 demultiplexer is ____________

- a)Q2.(Q1)’.Q0.I

- b)Q2.Q1.(Q0)’.I

- c)Q2.(Q1)’.(Q0)’.I

- d)Q2.(Q1).Q0.I

Correct answer is option 'C'. Can you explain this answer?

The output Q4 of this 1-to-8 demultiplexer is ____________

a)

Q2.(Q1)’.Q0.I

b)

Q2.Q1.(Q0)’.I

c)

Q2.(Q1)’.(Q0)’.I

d)

Q2.(Q1).Q0.I

| Gate Funda answered |

The output Y4 = S2.(S1)’.(S0)’.I. since the bit combinations of 4 are 100.

If (211)x = (152)8 , then the value of base x is- a)6

- b)5

- c)7

- d)9

Correct answer is option 'C'. Can you explain this answer?

If (211)x = (152)8 , then the value of base x is

a)

6

b)

5

c)

7

d)

9

| Baishali Bajaj answered |

2x^2 + x + 1 = 64 + 40 + 2

2x^2 + x + 1 = 106

x = 7

The output of a J-Kflip-flop with asynchronous preset and clear inputs if ‘1 ’. The output can be changed to ‘0’ with which one of the following conditions?- a)By applying J = 1, K= 0 and using the clock

- b)By applying a synchronous preset input

- c)By applying J = 1, K = 1 and using the clock

- d)By applying J = 0, K = 0 and using the clock

Correct answer is option 'C'. Can you explain this answer?

The output of a J-Kflip-flop with asynchronous preset and clear inputs if ‘1 ’. The output can be changed to ‘0’ with which one of the following conditions?

a)

By applying J = 1, K= 0 and using the clock

b)

By applying a synchronous preset input

c)

By applying J = 1, K = 1 and using the clock

d)

By applying J = 0, K = 0 and using the clock

| | Raj Desai answered |

When J = 1, K = 1 and the clock, next state will be complement of the present state. Thus,

Which IC is used for the implementation of 1-to-16 DEMUX?- a)IC 74154

- b)IC 74155

- c)IC 74139

- d)IC 74138

Correct answer is option 'A'. Can you explain this answer?

Which IC is used for the implementation of 1-to-16 DEMUX?

a)

IC 74154

b)

IC 74155

c)

IC 74139

d)

IC 74138

| | Mihir Chawla answered |

IC 74154 is used for the implementation of 1-to-16 DEMUX.

Explanation:

1-to-16 DEMUX is a digital circuit which takes one input and distributes it across the 16 output lines based on the input binary address. It is used in various applications such as memory addressing, data routing, and selection of input/output lines.

IC 74154 is a 4-to-16 decoder/demultiplexer IC with active-low outputs. It has 4 select inputs (A, B, C, D) and 16 output lines. Each output line corresponds to a unique combination of the select inputs. When a particular combination of select inputs is enabled, the corresponding output line goes low while all other output lines remain high.

To implement a 1-to-16 DEMUX using IC 74154, we can connect the input to one of the select inputs (e.g. A) and tie the remaining select inputs (B, C, D) to ground. This enables the output line corresponding to the input address (A=1) while keeping all other output lines high.

Therefore, IC 74154 is the correct choice for implementing a 1-to-16 DEMUX due to its multiple output lines and select inputs, making it suitable for addressing and routing applications.

Explanation:

1-to-16 DEMUX is a digital circuit which takes one input and distributes it across the 16 output lines based on the input binary address. It is used in various applications such as memory addressing, data routing, and selection of input/output lines.

IC 74154 is a 4-to-16 decoder/demultiplexer IC with active-low outputs. It has 4 select inputs (A, B, C, D) and 16 output lines. Each output line corresponds to a unique combination of the select inputs. When a particular combination of select inputs is enabled, the corresponding output line goes low while all other output lines remain high.

To implement a 1-to-16 DEMUX using IC 74154, we can connect the input to one of the select inputs (e.g. A) and tie the remaining select inputs (B, C, D) to ground. This enables the output line corresponding to the input address (A=1) while keeping all other output lines high.

Therefore, IC 74154 is the correct choice for implementing a 1-to-16 DEMUX due to its multiple output lines and select inputs, making it suitable for addressing and routing applications.

Three decade counter would have ____________- a)2 BCD counters

- b)3 BCD counters

- c)4 BCD counters

- d)5 BCD counters

Correct answer is option 'B'. Can you explain this answer?

Three decade counter would have ____________

a)

2 BCD counters

b)

3 BCD counters

c)

4 BCD counters

d)

5 BCD counters

| | Pankaj Mehta answered |

A decade counter is a circuit that counts in decimal (from 0 to 9) and is commonly used in digital electronics. It is often implemented using flip-flops and is used for a variety of applications, such as frequency division, time measurement, and sequencing.

Decade counters can be cascaded together to form larger counters with higher counting ranges. When cascading multiple decade counters, the output of one counter is connected to the clock input of the next counter. This allows the counters to count in a sequential manner, with each counter incrementing by 1 when the previous counter reaches its maximum value.

In the case of a three-decade counter, there are three individual decade counters connected in cascade. Each decade counter has four output lines, which can be used to represent the binary-coded decimal (BCD) equivalent of the count value. The BCD representation uses four bits to represent each decimal digit (0 to 9).

Since each decade counter has four output lines, it can represent values from 0 to 9 (2^4 = 16 possible combinations). Therefore, a single decade counter can count from 0 to 9. By cascading three decade counters together, we can extend the counting range from 0 to 999 (3 * 10^2 - 1).

To summarize, a three-decade counter consists of three individual decade counters cascaded together. Each individual decade counter can count from 0 to 9, and by combining them, we can count from 0 to 999. Therefore, a three-decade counter would have three BCD counters.

Decade counters can be cascaded together to form larger counters with higher counting ranges. When cascading multiple decade counters, the output of one counter is connected to the clock input of the next counter. This allows the counters to count in a sequential manner, with each counter incrementing by 1 when the previous counter reaches its maximum value.

In the case of a three-decade counter, there are three individual decade counters connected in cascade. Each decade counter has four output lines, which can be used to represent the binary-coded decimal (BCD) equivalent of the count value. The BCD representation uses four bits to represent each decimal digit (0 to 9).

Since each decade counter has four output lines, it can represent values from 0 to 9 (2^4 = 16 possible combinations). Therefore, a single decade counter can count from 0 to 9. By cascading three decade counters together, we can extend the counting range from 0 to 999 (3 * 10^2 - 1).

To summarize, a three-decade counter consists of three individual decade counters cascaded together. Each individual decade counter can count from 0 to 9, and by combining them, we can count from 0 to 999. Therefore, a three-decade counter would have three BCD counters.

Which of the following circuits can be used as a series to parallel converter?- a)Encoder

- b)Decoder

- c)De-multiplexer

- d)Multiplexer

Correct answer is option 'C'. Can you explain this answer?

Which of the following circuits can be used as a series to parallel converter?

a)

Encoder

b)

Decoder

c)

De-multiplexer

d)

Multiplexer

| | Pooja Patel answered |

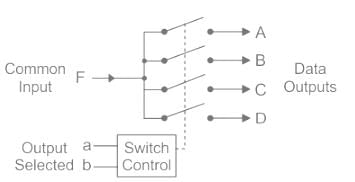

De-multiplexer:

- The demultiplexer is a combinational logic circuit designed to switch one common input line to one of several separate output lines.

- The data distributor, known as a Demultiplexer or “Demux”, works in just the opposite way to that of the Multiplexer.

- The demultiplexer takes one single input data line and then switches it to any one of a number of individual output lines one at a time.

The block diagram is as shown:

Application:

The demultiplexer converts a serial data signal at the input to parallel data at its output lines as shown below.

The function of the Demultiplexer is to switch one common data input line to any one of the 4 output data lines A to D.

Important:

Multiplexer:

The multiplexer is a combinational logic circuit designed to switch one of several input lines to a single common output line.

Application:

The demultiplexer converts a serial data signal at the input to parallel data at its output lines as shown below.

The function of the Demultiplexer is to switch one common data input line to any one of the 4 output data lines A to D.

Important:

Multiplexer:

The multiplexer is a combinational logic circuit designed to switch one of several input lines to a single common output line.

- The multiplexer or “MUX” is a combinational logic circuit designed to switch one of several input lines through a single common output line by the application of a control signal.

- Multiplexers operate like very fast acting multiple position rotary switches connecting or controlling multiple input lines called “channels” one at a time to the output.

- Multiplexers are used to convert parallel to serial data.

In 1-to-4 multiplexer, if C1 = 0 & C2 = 1, then the output will be ___________- a)Y0

- b)Y1

- c)Y2

- d)Y3

Correct answer is option 'B'. Can you explain this answer?

In 1-to-4 multiplexer, if C1 = 0 & C2 = 1, then the output will be ___________

a)

Y0

b)

Y1

c)

Y2

d)

Y3

| | Swati Tiwari answered |

If C1 = 0 in a 1-to-4 multiplexer, it means that the control input C1 is set to logic 0.

In a 1-to-4 multiplexer, there are two control inputs, C1 and C0, which select one of the four input lines to be connected to the output line. The control inputs are usually binary, meaning they can have a value of 0 or 1.

When C1 = 0, it specifies that the 0th input line is selected. This means that the output of the multiplexer will be the same as the signal on the 0th input line. The other input lines (1st, 2nd, and 3rd) are not connected to the output in this case.

In a 1-to-4 multiplexer, there are two control inputs, C1 and C0, which select one of the four input lines to be connected to the output line. The control inputs are usually binary, meaning they can have a value of 0 or 1.

When C1 = 0, it specifies that the 0th input line is selected. This means that the output of the multiplexer will be the same as the signal on the 0th input line. The other input lines (1st, 2nd, and 3rd) are not connected to the output in this case.

A decoder converts n inputs to __________ outputs.- a)n

- b)n2

- c)2n

- d)nn

Correct answer is option 'C'. Can you explain this answer?

A decoder converts n inputs to __________ outputs.

a)

n

b)

n2

c)

2n

d)

nn

| | Srishti Choudhary answered |

Decoder in Digital Electronics:

Decoders are essential components in digital electronics that convert n inputs into 2^n outputs. In other words, a decoder takes a binary-coded input and activates one of its outputs based on the input combination.

Explanation:

- Number of Outputs: The number of outputs in a decoder is determined by the number of inputs it has. For n inputs, a decoder will have 2^n outputs. This is because each input line can have two possible states (0 or 1), leading to 2^n possible combinations.

- Binary to Decimal Conversion: Decoders are often used to convert binary information to decimal. For example, a 2-input decoder can be used to decode binary numbers 00, 01, 10, and 11 to corresponding decimal numbers 0, 1, 2, and 3.

- Addressing Multiple Devices: Decoders are also used in address decoding in memory and input/output devices. By using a decoder, a microprocessor can select a specific device or memory location based on the address provided.

- Applications: Decoders are widely used in various digital systems such as multiplexers, demultiplexers, memory systems, arithmetic logic units, etc. They play a crucial role in data processing and control operations.

Conclusion:

In summary, a decoder converts n inputs to 2^n outputs, making it a versatile and fundamental component in digital electronics. Understanding the working principles of decoders is essential for designing and implementing complex digital systems.

Don’t care conditions can be used for simplifying Boolean expressions in ___________- a)Registers

- b)Terms

- c)K-maps

- d)Latches

Correct answer is option 'C'. Can you explain this answer?

Don’t care conditions can be used for simplifying Boolean expressions in ___________

a)

Registers

b)

Terms

c)

K-maps

d)

Latches

| | Mansi Choudhury answered |

I'm sorry, I don't understand what you are asking. Can you please provide more context or clarify your question?

Which of the following IC logic families has minimum value of fan-out? - a)ECL

- b)CMOS

- c)Low power Schottky TTL

- d)Standard TTL

Correct answer is option 'D'. Can you explain this answer?

Which of the following IC logic families has minimum value of fan-out?

a)

ECL

b)

CMOS

c)

Low power Schottky TTL

d)

Standard TTL

| | Harshad Singh answered |

Standard TTL logic family has the minimum value of fan-out compared to other options.

Standard TTL Logic Family:

- Standard TTL (Transistor-Transistor Logic) is a popular bipolar logic family known for its high speed and reliability.

- It has a fan-out value of around 10, which means that a single output can drive up to 10 inputs without affecting the performance.

- However, due to its higher power consumption and slower speed compared to other logic families like CMOS, it is less commonly used in modern applications.

ECL Logic Family:

- ECL (Emitter-Coupled Logic) is another high-speed logic family known for its superior performance in terms of speed and noise immunity.

- It typically has a higher fan-out value compared to standard TTL, making it suitable for high-speed applications where speed is critical.

CMOS Logic Family:

- CMOS (Complementary Metal-Oxide-Semiconductor) is a widely used logic family known for its low power consumption and high noise immunity.

- It has a higher fan-out value compared to standard TTL, making it suitable for applications where power efficiency is important.

Low Power Schottky TTL Logic Family:

- Low Power Schottky TTL is a variation of the TTL logic family designed to reduce power consumption while maintaining compatibility with standard TTL.

- It has a higher fan-out value compared to standard TTL but lower than CMOS, making it a good choice for applications that require a balance between power efficiency and speed.

What is a multiplexer?- a)It is a type of decoder which decodes several inputs and gives one output

- b)A multiplexer is a device which converts many signals into one

- c)It takes one input and results into many output

- d)It is a type of encoder which decodes several inputs and gives one output

Correct answer is option 'B'. Can you explain this answer?

What is a multiplexer?

a)

It is a type of decoder which decodes several inputs and gives one output

b)

A multiplexer is a device which converts many signals into one

c)

It takes one input and results into many output

d)

It is a type of encoder which decodes several inputs and gives one output

| | Prerna Tiwari answered |

Explanation:

A multiplexer is a device that combines multiple signals into one output signal. It is also known as a data selector, as it selects one of several input signals and forwards the selected signal to the output. The number of input signals can be two or more, and the selection of the input signal can be done through a control signal.

Working Principle:

The working principle of a multiplexer is based on the Boolean expression. A multiplexer has n input lines and one output line. The control signal selects which input to send to the output. The control signal is converted into a binary number, which is used to select one of the input lines.

Types of Multiplexers:

There are different types of multiplexers, including:

1. 2:1 Multiplexer: It has two input lines and one output line.

2. 4:1 Multiplexer: It has four input lines and one output line.

3. 8:1 Multiplexer: It has eight input lines and one output line.

Applications:

Multiplexers are used in various applications, including:

1. Communication systems: Multiplexers are used in communication systems to combine multiple signals into a single output signal.

2. Computer memory: Multiplexers are used in computer memory to select a particular memory cell.

3. Data transmission: Multiplexers are used in data transmission systems to select a particular data stream.

4. Digital circuit design: Multiplexers are used in digital circuit design to select an input signal based on a control signal.

Conclusion:

In conclusion, a multiplexer is a device that combines multiple signals into one output signal. It is widely used in various applications, including communication systems, computer memory, data transmission, and digital circuit design.

A multiplexer is a device that combines multiple signals into one output signal. It is also known as a data selector, as it selects one of several input signals and forwards the selected signal to the output. The number of input signals can be two or more, and the selection of the input signal can be done through a control signal.

Working Principle:

The working principle of a multiplexer is based on the Boolean expression. A multiplexer has n input lines and one output line. The control signal selects which input to send to the output. The control signal is converted into a binary number, which is used to select one of the input lines.

Types of Multiplexers:

There are different types of multiplexers, including:

1. 2:1 Multiplexer: It has two input lines and one output line.

2. 4:1 Multiplexer: It has four input lines and one output line.

3. 8:1 Multiplexer: It has eight input lines and one output line.

Applications:

Multiplexers are used in various applications, including:

1. Communication systems: Multiplexers are used in communication systems to combine multiple signals into a single output signal.

2. Computer memory: Multiplexers are used in computer memory to select a particular memory cell.

3. Data transmission: Multiplexers are used in data transmission systems to select a particular data stream.

4. Digital circuit design: Multiplexers are used in digital circuit design to select an input signal based on a control signal.

Conclusion:

In conclusion, a multiplexer is a device that combines multiple signals into one output signal. It is widely used in various applications, including communication systems, computer memory, data transmission, and digital circuit design.

Chapter doubts & questions for Digital Electronics - GATE Electrical Engineering (EE) Mock Test Series 2027 2026 is part of Electrical Engineering (EE) exam preparation. The chapters have been prepared according to the Electrical Engineering (EE) exam syllabus. The Chapter doubts & questions, notes, tests & MCQs are made for Electrical Engineering (EE) 2026 Exam. Find important definitions, questions, notes, meanings, examples, exercises, MCQs and online tests here.

Chapter doubts & questions of Digital Electronics - GATE Electrical Engineering (EE) Mock Test Series 2027 in English & Hindi are available as part of Electrical Engineering (EE) exam. Download more important topics, notes, lectures and mock test series for Electrical Engineering (EE) Exam by signing up for free.

Top Courses Electrical Engineering (EE)

Signup to see your scores go up within 7 days!

Access 1000+ FREE Docs, Videos and Tests

Takes less than 10 seconds to signup