NCERT Exemplar: Semiconductor Electronics | Physics Class 12 - NEET PDF Download

MULTIPLE CHOICE QUESTIONS I

Q.1. The conductivity of a semiconductor increases with increase in temperature because

(a) Number density of free current carriers increases

(b) Relaxation time increases

(c) Both number density of carriers and relaxation time increase

(d) Number density of current carriers increases, relaxation time decreases but effect of decrease in relaxation time is much less than increase in number density

Ans. (d)

Solution.

Key concept

Conductivity of Semiconductor:

(1) In intrinsic semiconductors ne = nh. Both electron and holes contributes in current conduction.

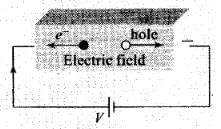

(2) When some potential difference is applied across a piece of intrinsic semiconductor current flows in it due to both electron and holes, i.e. i = ie + ih ⇒ i = eA[neve + nhvh]

(3) As we know  Hence conductivity of semiconductor is σ = e[neμe + nhμh]; where ve = drift velocity of electron, vh = drift velocity of holes, E= Applied electric field,

Hence conductivity of semiconductor is σ = e[neμe + nhμh]; where ve = drift velocity of electron, vh = drift velocity of holes, E= Applied electric field,  mobility of electron and

mobility of electron and  mobility of holes

mobility of holes

(4) Motion of electrons in the conduction band and of holes in the valence band under the action o f electric field is shown below:

(5) At absolute zero temperature (0 K)conduction band of semiconductor is completely empty, i.e., σ= 0. Hence the semiconductor behaves as an insulator.

We know that

So, σ ∝ nτ

where, n = number density and τ = relaxation time

In semiconductors conductivity increases with increase in temperature, because the number density of current carries increases, relaxation time decreases but effect of decrease in relaxation is much less than increase in number density.

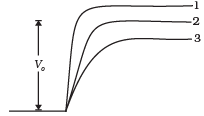

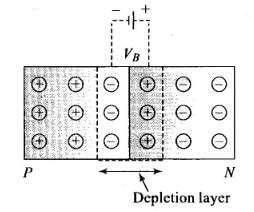

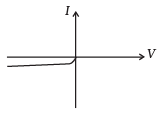

Q.2. In Figure, Vo is the potential barrier across a p-n junction, when no battery is connected across the junction

(a) 1 and 3 both correspond to forward bias of junction

(b) 3 corresponds to forward bias of junction and 1 corresponds to reverse bias of junction (c) 1 corresponds to forward bias and 3 corresponds to reverse bias of junction.

(d) 3 and 1 both correspond to reverse bias of junction.

Ans. (b)

when P-n junction is in forward bias, it compresses or decreases the depletion layer so potential barrier in forward bias decreases and in reverse layer so potential barrier in forward bias decrease and in reverse bias potential barrier increases.

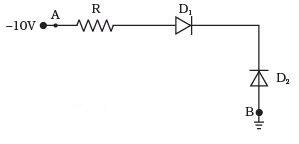

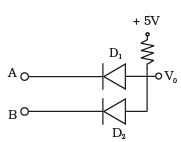

Q.3. In Figure assuming the diodes to be ideal,

(a) D1 is forward biased and D2 is reverse biased and hence current flows from A to B

(b) D2 is forward biased and D1 is reverse biased and hence no current flows from B to A and vice versa.

(c) D1 and D2 are both forward biased and hence current flows from A to B.

(d) D1 and D2 are both reverse biased and hence no current flows from A to B and vice versa.

Ans. (b)

Solution. A symbol of the diode is represented like this:

A symbol of the diode is represented like this:

In this problem first we have to check the polarity of the diodes. - 10 V is the lower, voltage in the circuit. Now p-side of p-n junction D1, is connected to lower voltage and n-side of D1 to higher voltage. Thus D1 is reverse biased.

Now, let us analyse 2nd diode of the given circuit. The p-side of p-n junction D2 is at higher potential and n-side of D2 is at lower potential. Therefore D2 is forward biased.

Hence, current flows through the junction from B to A.

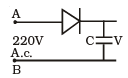

Q.4. A 220 V A.C. supply is connected between points A and B (in Figure). What will be the potential difference V across the capacitor?

(a) 220V

(b) 110V

(c) 0V

(d) 220√2 V

Ans. (d)

Solution.

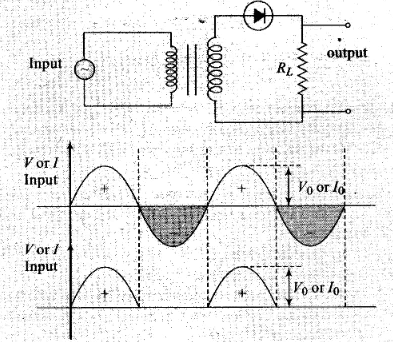

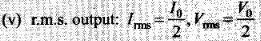

Key concept: Half wave rectifier: When the P-N junction diode rectifies half of the ac wave, it is called half wave rectifier.

(i) During positive half cycle,

Diode → forward biased

Output signal → obtained

(ii) During negative half cycle,

Diode → reverse biased

Output signal → not obtained

(iii) Output voltage is obtained across the load resistance RL. It is not constant but pulsating (mixture of ac and dc) in nature.

(iv) Average output in one cycle

(rf = forward biased resistance)

As p-n junction diode will conduct during positive half cycle only, during negative half cycle diode is reverse biased. During this diode will not give any output. So, potential difference across capacitor C - peak voltage of the given AC voltage

= V0 = Vrms√2 = 220√2 V

Q.5. Hole is

(a) An anti-particle of electron

(b) A vacancy created when an electron leaves a covalent bond

(c) Absence of free electrons

(d) An artifically created particle

Ans. (b)

Solution.

Concept of holes in the semiconductor:

- When an electron is removed from a covalent bond, it leaves a vacancy behind. An electron from a neighbouring atom can move into this vacancy, leaving the neighbour with a vacancy. In this way the vacancy formed is called a hole (or cotter), and can travel through the material and serve as an additional current carriers.

- A hole is considered as a seat of positive charge, having magnitude of charge equal to that of an electron.

- Holes acts as a virtual charge, although there is no physical charge on it.

- Effective mass of hole is more than an electron.

- Mobility of hole is less than an electron.

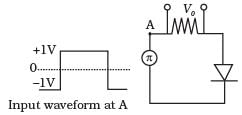

Q.6.The output of the given circuit in Figure

(a) Would be zero at all times

(b) Would be like a half wave rectifier with positive cycles in output

(c) Would be like a half wave rectifier with negative cycles in output

(d) Would be like that of a full wave rectifier

Ans. (c)

Solution.

When positive cycle is at A, diode will be in forward bias and resistance due to diode is approximately zero so potential across diode will be about zero.

Similarly, when there is negative half cycle at A, diode will be in reverse bias and resistance will be maximum so potential difference across diode is Vm sin ωt with negative at A.

So we get only negative output at A so it behaves like a half wave rectifier with negative cycle at A in output, verifies the answer (c).

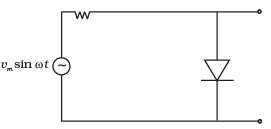

Q. 7. In the circuit shown in Figure, if the diode forward voltage drop is 0.3 V, the voltage difference between A and B is

(a) 1.3 V

(b) 2.3 V

(c) 0

(d) 0.5 V

Ans. (b)

Solution.

In the middle right of the circuit the capacitor behaves like an open circuit for d.c 0.2 mA current so current will flow from A to B only. Let potential across A and B is V, so by Kirchhoff’s loop law

VAB = (5000×0.2×10-3) +0.3+5000×0.2×10-3

VAB = 1V+0.3V+ 1V

VAB = 2.3 V

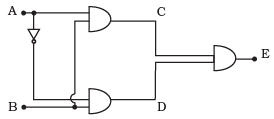

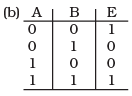

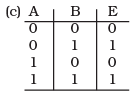

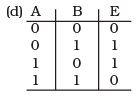

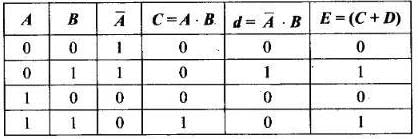

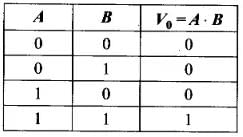

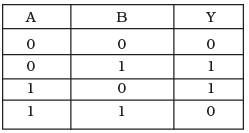

Q.8. Truth table for the given circuit (Figure) is

Ans. (c)

Solution.

In this problem the input C of OR gate and which is an output of AND gate. So, " equals A AND B" or C=A • B and "D equals Not A AND B" or

and “E equals C AND D" or E = C + D = (A . B) + (A . B)

Now we can generate the truth table of this arrangement of gates can be given by

MULTIPLE CHOICE QUESTIONS II

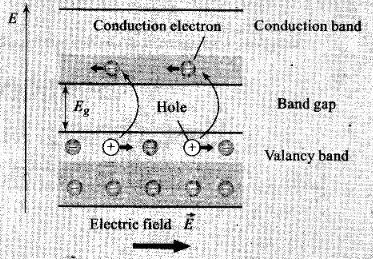

Q.9. When an electric field is applied across a semiconductor

(a) Electrons move from lower energy level to higher energy level in the conduction band

(b) Electrons move from higher energy level to lower energy level in the conduction band

(c) Holes in the valence band move from higher energy level to lower energy level

(d) Holes in the valence band move from lower energy level to higher energy level

Ans. (a,c)

Solution.

In valence band electrons are not capable of gaining energy from external electric field. While in conduction band the electrons can gain energy from external electric field.

When electric field is applied across a semiconductor, the electrons in the conduction band (which is partially filled with electrons) get accelerated and acquire energy. They move from lower energy level to higher energy level. While the holes in valence band move from higher energy level to lower energy level, where they will be having more energy.

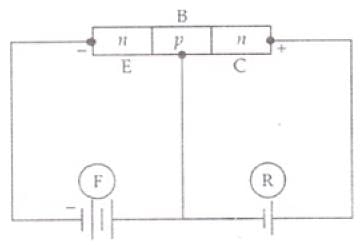

Q.10. Consider an npn transistor with its base-emitter junction forward biased and collector base junction reverse biased. Which of the following statements are true?.

(a) Electrons crossover from emitter to collector

(b) Holes move from base to collector

(c) Electrons move from emitter to base

(d) Electrons from emitter move out of base without going to the collector

Ans. (a,c)

Solution.

Electrons are repelled by forward bias from emitter to collector 5% of electrons combine with holes of base and rest 95% electrons of emitter are attracted by reverse bias of collector-base junction.

So electrons move from emitter to collector through base i.e., emitter to base verifies (a) and (c).

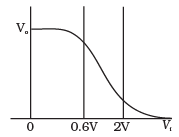

Q.11 Figure shows the transfer characteristics of a base biased CE transistor. Which of the following statements are true?

(a) At Vi = 0.4 V, transistor is in active state

(b) At Vi = 1 V , it can be used as an amplifier

(c) At Vi = 0.5 V, it can be used as a switch turned off

(d) At Vi = 2.5 V, it can be used as a switch turned on

Ans. (b,c,d)

Solution.

According to above graph transfer characteristics of a base biased common emitter transistor, we note that .

(a) when Vi= 0.4 V, output voltage remain same,there is no collection current. So, transistor circuit is not in active state.

(b) when Vi = 1 V (This is in between 0.6 V to 2 V), the transistor circuit is in active state and when input is increasing output is decreasing because when CE is used as an amplifier input and output voltages are 180° out of phase. Then it is used as an amplifier.

(c) when Vi = 0.5 V, there is no collector current. The transistor is in cut off state. The transistor circuit can be used as a switch to be turned off.

(d) when Vi = 2.5 V, the collector current becomes maximum and transistor is in a saturation state and can used as switch turned on state.

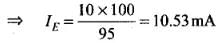

Q.12 In a npn transistor circuit, the collector current is 10 mA. If 95 per cent of the electrons emitted reach the collector, which of the following statements are true?

(a) The emitter current will be 8 mA

(b) The emitter current will be 10.53 mA

(c) The base current will be 0.53 mA

(d) The base current will be 2 mA

Ans. (b,c)

Solution.

According to the problem, the collector current is 95% of electrons reaching the collector after emission. And collector current, IC = 10 mA

IE = emitter current

Also,

Also, IB = IE - IC = 10.53 - 10 = 0.53 mA

Q.13. In the depletion region of a diode

(a) there are no mobile charges

(b) equal number of holes and electrons exist, making the region neutral

(c) recombination of holes and electrons has taken place

(d) immobile charged ions exist

Ans. (a,b,d)

Solution.

On account of difference in concentration of charge carrier in the two sections of P-N junction, the electrons from N-rcgion diffuse through the junction into P-region and the hole from P-region diffuse into N-region.

Due to diffusion, neutrality of both N-and P-type semiconductor is disturbed, a layer of negative charged ions appear near the junction in the P-crystal and a layer of positive ions appears near the junction in N-crystal. This layer is called depletion layer.

The thickness of depletion layer is 1 micron = 10-6 m.

Width of depletion layer ∞ 1/Dopping

Depletion is directly proportional to temperature.

Important point: The P-N junction diode is equivalent to capacitor in which the depletion layer acts as a dielectric.

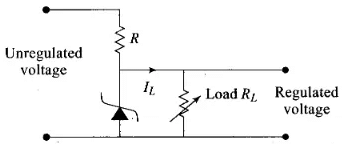

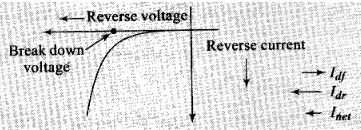

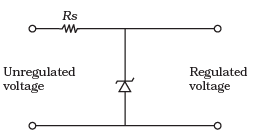

Q.14. What happens during regulation action of a Zener diode?

(a) The current in and voltage across the Zenor remains fixed

(b) The current through the series Resistance (Rs) changes

(c) The Zener resistance is constant

(d) The resistance offered by the Zener changes

Ans. (b, d)

Solution.

Symbolically zener diode represents like this:

In the forward bias, the zener diode acts as an ordinary diode. It can be used as a voltage regulator. Zener Diode as a voltage regulatorA zener diode when reverse biases offers constant voltage drop across in terminals as unregulated voltage is applied across circuit to regulate. Then during regulation action of a Zener diode, the current through the series resistance Rs changes and resistance offered by the Zener changes. The current through the Zener changes but the voltage across the Zener remains constant.

Zener Diode as a voltage regulatorA zener diode when reverse biases offers constant voltage drop across in terminals as unregulated voltage is applied across circuit to regulate. Then during regulation action of a Zener diode, the current through the series resistance Rs changes and resistance offered by the Zener changes. The current through the Zener changes but the voltage across the Zener remains constant.

Q.15. To reduce the ripples in a rectifier circuit with capacitor filter

(a) RL should be increased

(b) Input frequency should be decreased

(c) Input frequency should be increased

(d) Capacitors with high capacitance should be used

Ans. (a,c,d)

Solution.

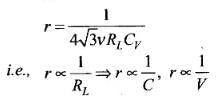

Ripple factor may be defined as the ratio of r.m.s. value of the ripple voltage to the absolute value of the DC component of the output voltage, usually expressed as a percentage. However ripple voltage is also commonly expressed as the peak-to-peak value. Ripple factor (r) of a full wave rectifier using capacitor filter is given by

Where, L is inductance of the coil and ω is the angular frequency.

or Ripple factor can also be given by

Ripple factor is inversely proportional to RL, C and v.

Thus to reduce r, RL should be increased, input frequency v should be increased and capacitance C should be increased.

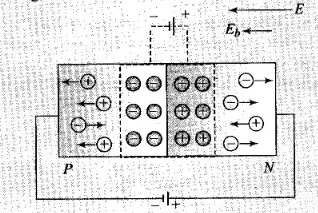

Q.16. The breakdown in a reverse biased p–n junction diode is more likely to occur due to (a) large velocity of the minority charge carriers if the doping concentration is small

(b) large velocity of the minority charge carriers if the doping concentration is large

(c) strong electric field in a depletion region if the doping concentration is small

(d) strong electric field in the depletion region if the doping concentration is large

Ans. (a,d)

Solution.

Reverse biasing: Positive terminal of the battery is connected to the N-crystal and negative terminal of the battery is connected to P-crystal.

(i) In reverse biasing width of depletion layer increases

(ii) In reverse biasing resistance offered RReverse = 105 Ω

(iii) Reverse bias supports the potential barrier and no current flows across the junction due to the diffusion of the majority carriers.

(A very small reverse current may exist in the circuit due to the drifting of minority carriers across the junction)

(iv) Break down voltage: Reverse voltage at which break down of semiconductor occurs. For Ge it is 25 V and for Si it is 35 V.

So, we conclude that in reverse biasing, ionization takes place because the minority charge carriers will be accelerated due to reverse biasing and striking with atoms which in turn cause secondary electrons and thus more number of charge carriers.

When doping concentration is large, there will be a large number of ions in the depletion region, which will give rise to a strong electric field.

Part- 2

Very Short Answer Type Questions

Q.17. Why are elemental dopants for Silicon or Germanium usually chosen from group XIII or group XV?

Ans. When pure semiconductor material is mixed with small amounts of certain specific impurities with valency different from that of the parent material, the number of mobile electrons/holes drastically changes. The process of addition of impurity is called doping. The size of the dopant atom should be compatible such that their presence in the pure semiconductor does not distort the semiconductor but easily contribute the charge carriers on forming covalent bonds with Silicon or Germanium atoms, which are provided by group XIII or group XV elements.

Q.18. Sn, C, and Si, Ge are all group XIV elements. Yet, Sn is a conductor, C is an insulator while Si and Ge are semiconductors. Why?

Ans. The conduction level of any element depends on the energy gap between its conduction band and valence band.

In conductors, there is no energy gap between conduction band and valence band. For insulator, the energy gap is large and for semiconductor the energy gap is moderate.

The energy gap for Sn is 0 eV, for C is 5.4 eV, for Si is 1.1 eV and for Ge is 0.7 eV related to their atomic size. Therefore Sn is a conductor, C is an insulator, and Ge and Si are semiconductors

Q.19. Can the potential barrier across a p-n junction be measured by simply connecting a voltmeter across the junction?

Ans. We cannot measure the potential barrier across a p-n junction by a voltmeter because the resistance of voltmeter is very high as compared to the junction resistance. Potential of potential barrier for Ge is VB = 0.3 V and for silicon is VB = 0.7 V.

On the average the potential barrier in P-N junction is ~0.5 V.

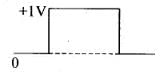

Q.20. Draw the output waveform across the resistor (Figure). Ans. The diode act as a half wave rectifier, it offers low resistance when forward biased and high resistance when reverse biased. So the output is obtained only when positive input is given,so the output waveform is

Ans. The diode act as a half wave rectifier, it offers low resistance when forward biased and high resistance when reverse biased. So the output is obtained only when positive input is given,so the output waveform is

Q.21. The amplifiers X, Y and Z are connected in series. If the voltage gains of X, Y and Z are 10, 20 and 30, respectively and the input signal is 1 mV peak value, then what is the output signal voltage (peak value)

(i) if dc supply voltage is 10V?

(ii) if dc supply voltage is 5V?

Ans. Total voltage amplification is defined as the ratio of output signal voltage and input signal voltage.

According to the problem, voltage gain in X, vx = 10,

voltage gain in Y; vy = 20,

voltage gain in Z, vz, = 30;

ΔVi = 1 mV = 10-3 V

And Total voltage amplification = vx * vy * vz,

ΔV0 = vx * vy * vz * ΔVi

= 10 *20 * 30 * 10-3 = 6V

(i) If DC supply voltage is 10 V, then output is 6 V, since theoretical gain is equal to practical gain, i.e., output can never be greater than 6 V.

(ii) If DC supply voltage is 5 V, i.e., Vcc = 5 V. Then, output peak will not exceed 5 V. Hence V0 = 5 V.

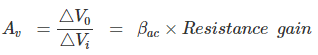

Q.22. In a CE transistor amplifier there is a current and voltage gain associated with the circuit. In other words there is a power gain.

Considering power a measure of energy, does the circuit violate conservation of energy?

Ans.

Key Concept: Different gain in CE transistor amplifier.

(i) ac current gain:

(ii) dc current gain :

(iii) Voltage gain:

(iv) Power gain:

The power gain is very high in CE transistor amplifier. In this circuit, the extra power required for amplified output is obtained from DC source. Thus, the circuit used does not violate the law of conservation.

SHORT ANSWER TYPE QUESTIONS

Q.23.

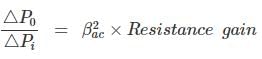

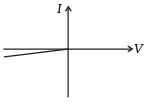

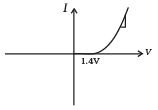

(i) Name the type of a diode whose characteristics are shown in Figure (A) and Fig. (B).

(i) Name the type of a diode whose characteristics are shown in Figure (A) and Fig. (B).

(ii) What does the point P in Figure (A) represent?

(iii) What does the points P and Q in Figure (B) represent?

Ans.

(i) Figure (a) represents the characteristics of Zener diode and curve (b) is of solar cell.

(ii) In figure (a), point P represents Zener breakdown voltage.

(iii) In figure (b), the point Q represents zero voltage and negative current. Which means the light falling on solar cell with atleast minimum threshold frequency gives the current in opposite direction to that due to a battery connected to solar cell. But for the point Q the battery is short circuited. Hence it represents the short circuit current.

And the point Pin figure (b) represents some open circuit, voltage on solar cell with zero current through solar cell.

It means, there is a battery connected to a solar cell which gives rise to the equal and opposite current to that in solar cell by virtue of light falling on it.

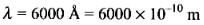

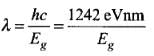

Q.24. Three photo diodes D1, D2 and D3 are made of semiconductors having band gaps of 2.5 eV, 2 eV and 3 eV, respectively. Which ones will be able to detect light of wavelength  ?

?

Ans.  According to the problem,

According to the problem,

Wavelength of light

energy of the light photon

The incident radiation which is detected by the photodiode D2 because energy of incident radiation is greater than the band-gap.

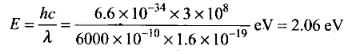

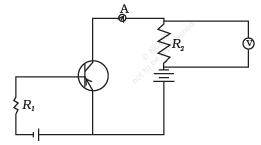

Q.25. If the resistance R1 is increased (Figure), how will the readings of the ammeter and voltmeter change? Ans. Let us redrawn the circuit diagram to find the change in reading of ammeter and voltmeter.

Ans. Let us redrawn the circuit diagram to find the change in reading of ammeter and voltmeter. so, IBR1 + VBE = VBB

so, IBR1 + VBE = VBB

Basic current

So, R1 is increased, IB is decreased.

Now, the current in ammeter is collector current IC.

IC = βIB as IB is decreased, IC is also decreased and the reading of voltmeter and ammeter also decreased.

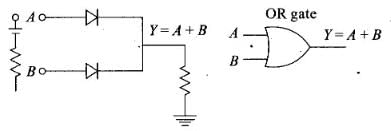

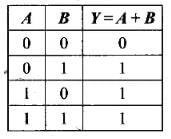

Q.26. Two car garages have a common gate which needs to open automatically when a car enters either of the garages or cars enter both. Devise a circuit that resembles this situation using diodes for this situation.

Ans. As car enters in either of the garages or both, the common gate opened automatically.

This means that if any one input is high, output will high otherwise low.

The device is shown like this: So, OR gate gives the desired output

So, OR gate gives the desired output

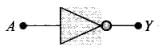

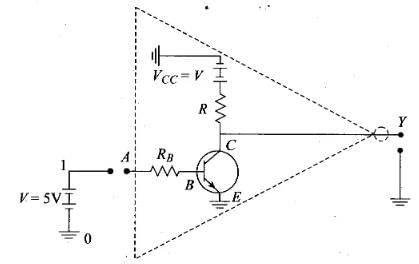

Q.27. How would you set up a circuit to obtain NOT gate using a transistor?

Ans.

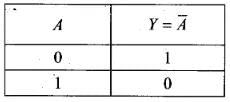

(1) It has only one input and only one output.

(2) Boolean expression is Y = Ᾱ and is read as “y equals not A” .

Logical symbol of NOT gate.  (3) Realization of NOT gate: The transistor is so biased that the collector voltage VCC = V (Voltage corresponding to 1 state)

(3) Realization of NOT gate: The transistor is so biased that the collector voltage VCC = V (Voltage corresponding to 1 state)

The resistors R and RB are so chosen that if the input is low, i.e. 0, the transistor is in the cut off and hence the voltage appearing at the output will be the same as applied V = 5 V. Hence Y = V(or state I)

If the input is high, the transistor current is in saturation and the net voltage at the output Y is 0 (in state 0)  (4) Truth table for Not gate:

(4) Truth table for Not gate:

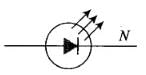

Q.28. Explain why elemental semiconductor cannot be used to make visible LEDs.

Ans. Specially designed diodes, which give out light radiations when forward biases. LED 's are made of GaAsp, Gap etc.

Specially designed diodes, which give out light radiations when forward biases. LED 's are made of GaAsp, Gap etc.

These are forward biased P-N junctions which emits spontaneous radiation.

In elemental semiconductor, the band gap is such that the emission arc in infrared region and not in visible region.

for Si; Eg = 1.1 eV, λ = 1242/1.1 = 1129 nm

for Ge; Eg = 0.7 eV, λ = 1242/0.7 = 1725 nm

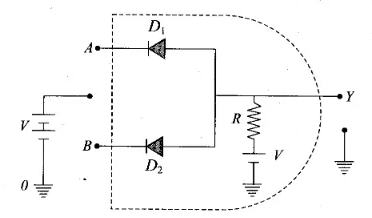

Q.29. Write the truth table for the circuit shown in Figure. Name the gate that the circuit resembles. Ans.

Ans. Logical Symbol of AND gateThis is 'AND' Gate and its characteristics are as follows:

Logical Symbol of AND gateThis is 'AND' Gate and its characteristics are as follows:

(1) it has two inputs (A and B) and only one output (Y)

(2) Boolean expression is Y = A.B is read as "Y equals A AND B"

(3) Realization of AND gate

(i) A = 0 , B = 0

The voltage supply through R is forward biasing diodes D1 and D2 (offers low resistance), the voltage V would drop across R.

The output voltage at Y= the voltage across diode = 0

(ii) A = 0, B = I

D1 = Conducts, D2 = Not Conducts

The out voltage at Y= The voltage across the diode (D2) = 0

(iii) A = 1 , B = 0

D1 = Conducts, D2 = Not conducts

The out voltage at Y= The voltage across the diode (D2) = 0

(iv) A = 1 , B = 1

None of the diode conducts

The out voltage at Y= Battery voltage = I

(4) Truth table for ‘AND' gate

Q.30. A Zener of power rating 1 W is to be used as a voltage regulator. If zener has a breakdown of 5V and it has to regulate voltage which fluctuated between 3V and 7V, what should be the value of Rs for safe operation (Figure)?

Ans.

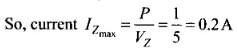

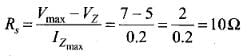

According to the problem power = 1 W

Zener breakdown voltage, Vz = 5 V

Minimum voltage, Vmin = 3 V

Maximum voltage, Vmax = 7 V

We know, P = VI

for safe operations Rs will be equal to

Long Answer Type Questions

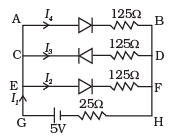

Q.31. If each diode in Figure has a forward bias resistance of 25Ω and infinite resistance in reverse bias, what will be the values of the current I1, I2, I3 and I4?

Ans.

According to the problem, forward biased resistance = 25 Ω and reverse biased resistance = ∞.

As shown in the figure, the diode in branch CD is in reverse biased which having infinite resistance.

So, current in that branch is zero, i.e. I3 = 0

Resistance in branch AB = 25 + 125 = 150 Ω, say R1

Resistance in branch EF - 25 + 125 = 150 Ω, say R2

AB is parallel to EF.

So, effective resistance

⇒ R' = 75Ω

Total resistance R of the circuit - R' + 25 = 75 + 25 = 100 U.

According to the kirchoff’s, current law (K.CL),

I1=I4 + I2 + I3 (Here I3 = 0)

So, I1 = I4 + I2

Here, the resistances R1 and R2 is same.

i.e., I4 = I2

∴ I1 = 2I2

and I4 = 0.025 A

Therefore, we get, I1, = 0.05 A, I2 = 0.025 A, I3 = 0 and I4 = 0.025 A

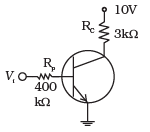

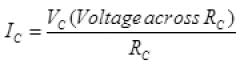

Q.32. In the circuit shown in Figure when the input voltage of the base resistance is 10 V, Vbe is zero and Vce is also zero. Find the values of Ib, Ic and β.

Ans. Voltage across RB = 10V

VB = RBIB

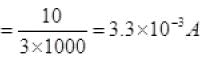

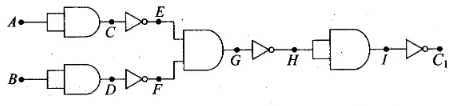

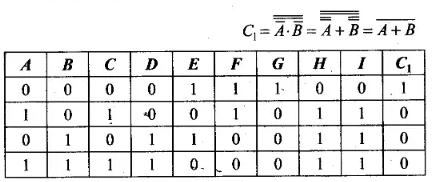

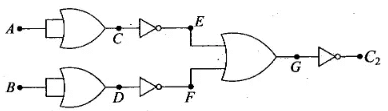

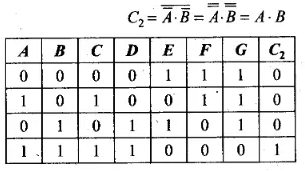

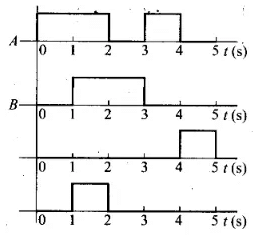

Q.33 Draw the output signals C1 and C2 in the given combination of gates (Figure).

Ans.

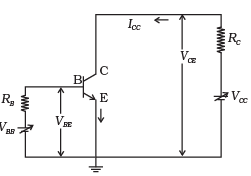

Q.34. Consider the circuit arrangement shown in Figure (a) for studying input and output characteristics of npn transistor in CE configuration. (a)

(a)

(b)

(b)

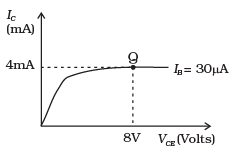

Select the values of RB and RC for a transistor whose VBE = 0.7 V, so that the transistor is operating at point Q as shown in the characteristics shown in Figure (b).

Given that the input impedance of the transistor is very small and VCC = VBB = 16 V, also find the voltage gain and power gain of circuit making appropriate assumptions.

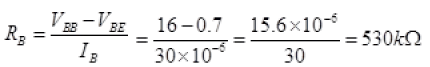

Ans. For output characteristic at point Q

VCE = 8V, IB = 30 μA, IC = 4 mA, VBE = 0.7V

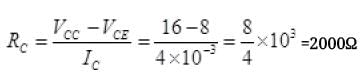

Applying Kirchhoff’s law in collector-emitter loop

VCC=VCE+RCIC

RC= 2000Ω

Now applying Kirchhoff’s loop law in base-emitter circuit,

VBB=IBRB + VBE

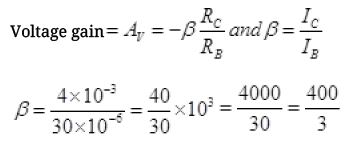

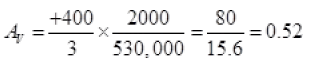

Average Voltage AV

(-) sign shows change in phase angle of output is by input voltage.

Power gain = I.V

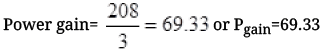

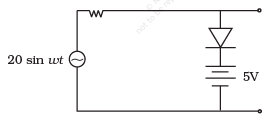

Q.35. Assuming the ideal diode, draw the output waveform for the circuit given in Figure Explain the waveform.

Ans.

Key concept: An ideal diode is a diode in which it has a very large resistance in reverse biased and very, low resistance in forward biased. So, it acts like a perfect conductor when voltage is applied forward biased and like a perfect insulator when voltage is applied reverse biased.

In reverse biased when the input voltage is equal to or less than 5 V diode,then it will offer high resistance in comparison to resistance (R) in series. Now, diode appears in open circuit. The input waveform is then passed to the output terminals. The result with sin wave input is to dip off all positive going portion above 5 V.

If input voltage is greater than +5 V, diode is in conducting state, then it will be conducting as if forward biased offering low resistance in comparison to R. But there will be no voltage in output beyond 5 V as the voltage beyond +5 V will appear across R.

When input voltage is negative, there will be opposition to 5 V battery in p-n junction input voltage becomes more than -5 V, the diode will be reverse biased. It will offer high resistance in comparison to resistance R in series. Now junction diode appears in open circuit. The input wave form is then passed on to the output terminals.

The output waveform will be like this (as shown below).

Q.36. Suppose a ‘n’-type wafer is created by doping Si crystal having 5 × 1028 atoms/m3 with 1ppm concentration of As. On the surface 200 ppm Boron is added to create ‘P’ region in this wafer. Considering nt = 1.5 × 1016 m–3,

(i) Calculate the densities of the charge carriers in the n & p regions.

(ii) Comment which charge carriers would contribute largely for the reverse saturation current when diode is reverse biased.

Ans.

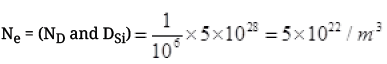

When As (pentavalent) is added to Si the n-type water is created.

So the number of majority carriers in n-type water,

For number of minority carriers nh

=0.3 × 1.5 × 1032-22 = 0.45 × 10+10 perm3

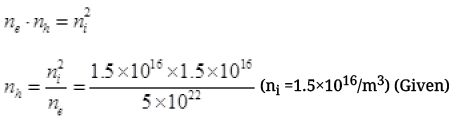

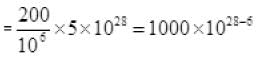

When boron(trivalent) is implanted in Si crystal, p- type wafer is formed with number of holes,

nh = (ND × n of Si)

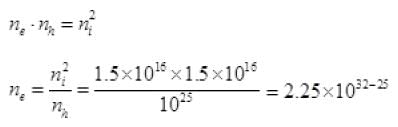

nh = 1×1025 per m3

Minority carrier in p-type water

=2.25 × 107 electrons per m3

When reversed bias is applied on p-n junction then the minority charge carrier moves toward depletion layer i.e., holes nh=(0.45×1010 per m3) from n side and ne=2.25 × 107/m3 from p side moves towards junction and make the depletion layer thicker.

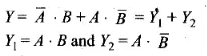

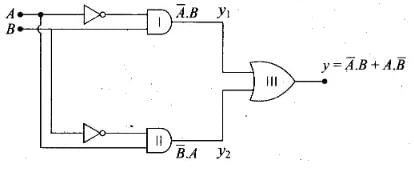

Q.37 An X-OR gate has following truth table:

It is represented by following logic relation

Build this gate using AND, OR and NOT gates.

Ans. XOR gate can be realized by the combination of two NOT gates, two AND gates and one OR gate. According to the problem, the logic relation for the . given truth table is

When

Y1 can be obtained as output of AND gate I for which one input is of A through NOT gate and another input is of B. Y2 can be obtained as output of AND gate II for which one input is of A and other input is of B through NOT gate.

Now Y can be obtained as output from OR gate, where Y1, and Y2 are inputs of OR gate.

Thus, the logic circuit of this relation is given below.

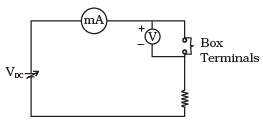

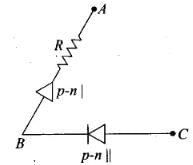

Q.38. Consider a box with three terminals on top of it as shown in Figure (a): (a)

(a)

Three components namely, two germanium diodes and one resistor are connected across these three terminals in some arrangement.

A student performs an experiment in which any two of these three terminals are connected in the circuit shown in (b). (b)The student obtains graphs of current-voltage characteristics for unknown combination of components between the two terminals connected in the circuit.

(b)The student obtains graphs of current-voltage characteristics for unknown combination of components between the two terminals connected in the circuit.

The graphs are

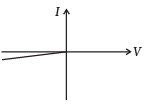

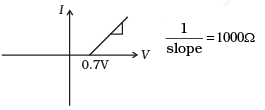

(i) when A is positive and B is negative (c)(ii) when A is negative and B is positive

(c)(ii) when A is negative and B is positive

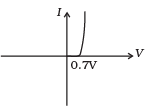

(d)(iii) When B is negative and C is positive

(d)(iii) When B is negative and C is positive (e)(iv) When B is positive and C is negative

(e)(iv) When B is positive and C is negative (f)(v) When A is positive and C is negative

(f)(v) When A is positive and C is negative (g)(vi) When A is negative and C is positive

(g)(vi) When A is negative and C is positive (h)From these graphs of current – voltage characteristic shown in Figure (c) to (h), determine the arrangement of components between A, B and C.

(h)From these graphs of current – voltage characteristic shown in Figure (c) to (h), determine the arrangement of components between A, B and C.

Ans. The V-I characteristics of these graph is discussed in points:

(a) In V-I graph of condition (i), a reverse characteristics is shown in figure (c). Here A is connected to n-side of p-n junction I and B is connected top-side of p-n junction I with a resistance in series.

(b) In V-I graph of condition (ii), a forward characteristics is shown in figure (d), where 0.7 V is the knee voltage of p-n junction I. 1/slope = (1/1000) Ω.

It means A is connected to n-side of p-n junction I and B is connected to p-side of p-n junction I and resistance R is in series of p-n junction I between A and B.

(c) In V-I graph of condition (iii), a forward characteristics is shown in figure (e) , where 0.7 V is the knee voltage. In this case p-side of p-n junction II is connected to C and n-side of p-n junction II to B.

(d) In V-I graphs of conditions (iv), (v), (vi) also concludes the above connection of p-n junctions I and II along with a resistance R.

Thus, the arrangement of p-n I, p-n II and resistance R between A, B and C will be as shown in the figure.

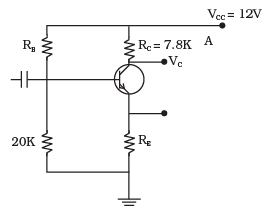

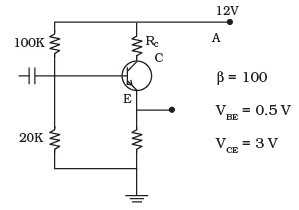

Q.39. For the transistor circuit shown in Figure, evaluate VE, RB, RE given IC = 1 mA, VCE = 3V, VBE = 0.5 V and VCC = 12 V, β = 100.

Ans. Let us redraw the circuit diagram given here to solve this problem.

As we know the base current is very small. So,

As we know the base current is very small. So,

Ic ≈ IE

Rc = 7.8 kΩ

From the figure, IC(RC + RE) + VCE = 12

(RE + RC) x 1 x 10-3 + 3= 1 2

RE + RC = 9 x I03 = 9 k Ω

RE = 9 - 7.8 = 1.2 kΩ

VE = IE x RE

= l x 10-3 x 1.2 x 103 = 1.2 V

Voltage VB = VE +VBE= 1. 2+ 0.5 = 1.7 V

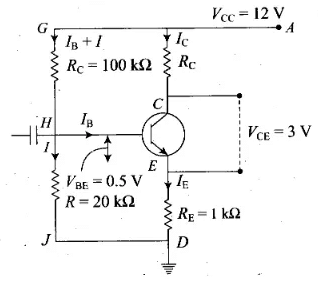

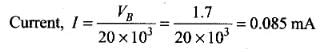

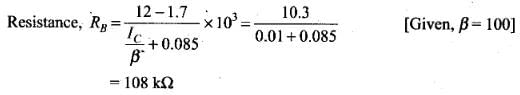

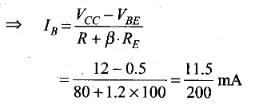

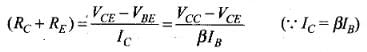

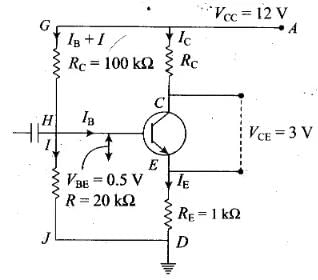

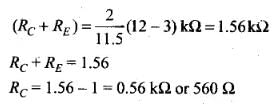

Q.40. In the circuit shown in Figure, find the value of RC.

Ans. Let us consider the circuit diagram to solve this problem,

IE = IC + IB and IC = βIB ..(i)

ICRC + VCE + IERE = VCC ..(ii)

RIB + VBE + IERE = VCC ..(iii)

∴ IE≈IC = βIB

from (iii)

(R + βRE)IB = VCC - VBE

from (ii),

|

74 videos|314 docs|88 tests

|

FAQs on NCERT Exemplar: Semiconductor Electronics - Physics Class 12 - NEET

| 1. What is a semiconductor? |  |

| 2. How do semiconductors work in electronic devices? |  |

| 3. What is the difference between an n-type and p-type semiconductor? |  |

| 4. What are the advantages of using semiconductors in electronic devices? |  |

| 5. How are semiconductors manufactured? |  |