All Exams > Electrical Engineering (EE) > 6 Months Preparation for GATE Electrical > All Questions

All questions of Sequential Circuits for Electrical Engineering (EE) Exam

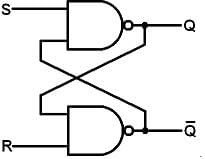

The circuits of NOR based S-R latch classified as asynchronous sequential circuits, why?- a)Because of inverted outputs

- b)Because of triggering functionality

- c)Because of cross-coupled connection

- d)Because of inverted outputs & triggering functionality

Correct answer is option 'C'. Can you explain this answer?

The circuits of NOR based S-R latch classified as asynchronous sequential circuits, why?

a)

Because of inverted outputs

b)

Because of triggering functionality

c)

Because of cross-coupled connection

d)

Because of inverted outputs & triggering functionality

| Advait Verma answered |

Introduction to NOR-Based S-R Latch

A NOR-based Set-Reset (S-R) latch is a fundamental building block in digital electronics, classified as an asynchronous sequential circuit. The classification stems from its inherent characteristics and operational mechanisms.

Understanding Asynchronous Sequential Circuits

- Definition: Asynchronous sequential circuits are those that do not rely on a clock signal for state changes. Instead, they change states based on input signals directly.

- Key Feature: The output of such circuits can change immediately in response to changes in input, making them asynchronous.

Why Cross-Coupled Connections Matter

- Cross-Coupled Configuration: The S-R latch utilizes feedback through cross-coupled NOR gates. This configuration enables the circuit to maintain its state until a new input is applied.

- State Retention: When one of the inputs (Set or Reset) is activated, it alters the state of the output. The feedback loop maintains this state even after the input is removed, underscoring the asynchronous nature.

Other Considerations

- Inverted Outputs: Although the outputs of a NOR gate are inverted, this alone does not classify the latch as asynchronous.

- Triggering Functionality: While triggering is relevant, it is not the primary reason for labeling the latch as asynchronous.

Conclusion

In summary, the cross-coupled connections in a NOR-based S-R latch are the primary reason for its classification as an asynchronous sequential circuit. The feedback mechanism allows the latch to change states based solely on input changes, independent of a clock signal.

A NOR-based Set-Reset (S-R) latch is a fundamental building block in digital electronics, classified as an asynchronous sequential circuit. The classification stems from its inherent characteristics and operational mechanisms.

Understanding Asynchronous Sequential Circuits

- Definition: Asynchronous sequential circuits are those that do not rely on a clock signal for state changes. Instead, they change states based on input signals directly.

- Key Feature: The output of such circuits can change immediately in response to changes in input, making them asynchronous.

Why Cross-Coupled Connections Matter

- Cross-Coupled Configuration: The S-R latch utilizes feedback through cross-coupled NOR gates. This configuration enables the circuit to maintain its state until a new input is applied.

- State Retention: When one of the inputs (Set or Reset) is activated, it alters the state of the output. The feedback loop maintains this state even after the input is removed, underscoring the asynchronous nature.

Other Considerations

- Inverted Outputs: Although the outputs of a NOR gate are inverted, this alone does not classify the latch as asynchronous.

- Triggering Functionality: While triggering is relevant, it is not the primary reason for labeling the latch as asynchronous.

Conclusion

In summary, the cross-coupled connections in a NOR-based S-R latch are the primary reason for its classification as an asynchronous sequential circuit. The feedback mechanism allows the latch to change states based solely on input changes, independent of a clock signal.

A serial in/parallel out, 4-bit shift register initially contains all 1s. The data nibble 0111 is waiting to enter. After four clock pulses, the register contains ________- a)0000

- b)1111

- c)0111

- d)1000

Correct answer is option 'C'. Can you explain this answer?

A serial in/parallel out, 4-bit shift register initially contains all 1s. The data nibble 0111 is waiting to enter. After four clock pulses, the register contains ________

a)

0000

b)

1111

c)

0111

d)

1000

| Pioneer Academy answered |

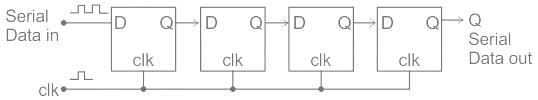

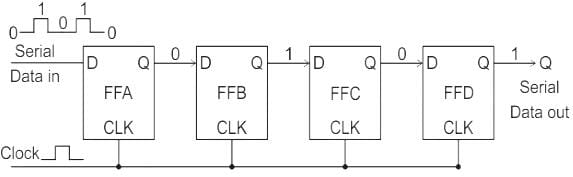

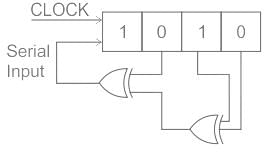

In Serial-In/Parallel-Out shift register, data will be shifted all at a time with every clock pulse. Therefore,

Wait | Store

0111 | 0000

011 | 1000 1st clk

01 | 1100 2nd clk

0 | 1110 3rd clk

X | 1111 4th clk.

Wait | Store

0111 | 0000

011 | 1000 1st clk

01 | 1100 2nd clk

0 | 1110 3rd clk

X | 1111 4th clk.

Assume that a 4-bit serial in/serial out shift register is initially clear. Bits are shifted in from left. We wish to store the nibble 1100. What will be the 4-bit pattern after the second clock pulse?- a)1100

- b)0011

- c)1111

- d)0000

Correct answer is option 'D'. Can you explain this answer?

Assume that a 4-bit serial in/serial out shift register is initially clear. Bits are shifted in from left. We wish to store the nibble 1100. What will be the 4-bit pattern after the second clock pulse?

a)

1100

b)

0011

c)

1111

d)

0000

| Cstoppers Instructors answered |

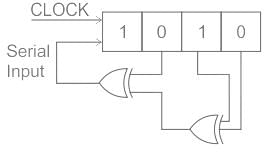

The register is given serial input with serial data 1100, the shift register is initially cleared 0000.

Since we have to store 1100 in the register, bits will be entered from the right.

The contents of the register after 1st pulse 0000.

Similarly, after the second shift, the contents of the register are 0000.

After the third clock pulse, the contents will be 1000

and after the fourth clock pulse, the contents will be 1100

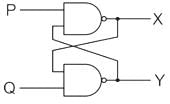

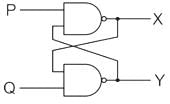

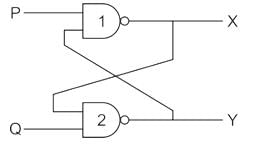

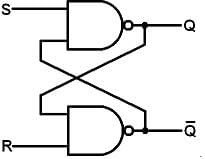

In the latch circuit shown, the NAND gates have non-zero, but unequal propagation delays. The present input conditions is: P = Q = ‘0’. If the input conditions is changed simultaneously to P = Q = ‘1’, the outputs X and Y are

- a)X = ‘1’, Y = ‘1’

- b)either X = ‘1’, Y = ‘0’ or X = ‘0’, Y = ‘1’

- c)either X = ‘1’, Y = ‘1’ or X = ‘0’, Y = ‘0’

- d)X = ‘0’, Y = ‘0’

Correct answer is option 'B'. Can you explain this answer?

In the latch circuit shown, the NAND gates have non-zero, but unequal propagation delays. The present input conditions is: P = Q = ‘0’. If the input conditions is changed simultaneously to P = Q = ‘1’, the outputs X and Y are

a)

X = ‘1’, Y = ‘1’

b)

either X = ‘1’, Y = ‘0’ or X = ‘0’, Y = ‘1’

c)

either X = ‘1’, Y = ‘1’ or X = ‘0’, Y = ‘0’

d)

X = ‘0’, Y = ‘0’

| | Pooja Patel answered |

Let as assume tpd 1 < tpd 2

x changes state first then y changes

1st output of X (P = 1, y = 0) ⇒ X1 = 1

Next output of Y (Q = 1, X1 = 1) ⇒ Y1 = 0

2nd output of X (P = 1, y1 = 0) ⇒ 1

Hence output x = 1 y = 0 (if tpd1 < tpd2)

& Output X = 0 Y = 1 (if tpd2 < tpd1)

The S-R, J-K and D inputs are called ____________- a)Asynchronous inputs

- b)Synchronous inputs

- c)Bidirectional inputs

- d)Unidirectional inputs

Correct answer is option 'B'. Can you explain this answer?

The S-R, J-K and D inputs are called ____________

a)

Asynchronous inputs

b)

Synchronous inputs

c)

Bidirectional inputs

d)

Unidirectional inputs

| | Sandeep Saha answered |

Asynchronous Inputs:

The S-R (Set-Reset), J-K (Jump-Kill), and D (Data) inputs are known as synchronous inputs. These inputs are commonly used in digital circuits, such as flip-flops and memory elements, to control the behavior and state of the circuit.

Synchronous Inputs:

The term "synchronous" refers to the fact that these inputs are synchronized with a clock signal. In synchronous circuits, the clock signal is used to control the timing and sequencing of the circuit's operations. The state of the circuit is only updated when a clock edge occurs, ensuring that all changes happen simultaneously.

Differences between Synchronous and Asynchronous Inputs:

1. Timing: Synchronous inputs are synchronized with the clock signal and change their state only at specific clock edges. Asynchronous inputs, on the other hand, can change their state independently of the clock signal.

2. Simultaneity: Synchronous inputs ensure that all changes happen simultaneously, as they are updated together during the clock edge. Asynchronous inputs do not guarantee this simultaneous behavior and can introduce timing hazards or glitches.

3. Stability: Synchronous inputs are typically edge-triggered, meaning they are stable and will not change their state until the next clock edge. Asynchronous inputs can be level-triggered, meaning their state can change and propagate through the circuit at any time.

4. Design Complexity: Synchronous designs are generally easier to analyze and implement since the timing behavior is well-defined and predictable. Asynchronous designs require additional considerations, such as handling metastability issues and ensuring proper timing constraints.

Importance of Synchronous Inputs:

Synchronous inputs provide a structured and predictable way to control the operation of digital circuits. By using a clock signal, the circuit can be designed to perform specific actions at specific times. This allows for more reliable and consistent behavior, especially in complex systems where numerous signals need to be coordinated.

In contrast, asynchronous inputs can introduce unpredictable behavior and can be challenging to analyze and debug. They are typically used in specialized cases where specific timing requirements or functionality necessitate their use.

In conclusion, S-R, J-K, and D inputs are called synchronous inputs because they are synchronized with a clock signal and change their state only at specific clock edges. Synchronous inputs provide a structured and predictable way to control the behavior and timing of digital circuits, ensuring reliable and consistent operation.

The S-R (Set-Reset), J-K (Jump-Kill), and D (Data) inputs are known as synchronous inputs. These inputs are commonly used in digital circuits, such as flip-flops and memory elements, to control the behavior and state of the circuit.

Synchronous Inputs:

The term "synchronous" refers to the fact that these inputs are synchronized with a clock signal. In synchronous circuits, the clock signal is used to control the timing and sequencing of the circuit's operations. The state of the circuit is only updated when a clock edge occurs, ensuring that all changes happen simultaneously.

Differences between Synchronous and Asynchronous Inputs:

1. Timing: Synchronous inputs are synchronized with the clock signal and change their state only at specific clock edges. Asynchronous inputs, on the other hand, can change their state independently of the clock signal.

2. Simultaneity: Synchronous inputs ensure that all changes happen simultaneously, as they are updated together during the clock edge. Asynchronous inputs do not guarantee this simultaneous behavior and can introduce timing hazards or glitches.

3. Stability: Synchronous inputs are typically edge-triggered, meaning they are stable and will not change their state until the next clock edge. Asynchronous inputs can be level-triggered, meaning their state can change and propagate through the circuit at any time.

4. Design Complexity: Synchronous designs are generally easier to analyze and implement since the timing behavior is well-defined and predictable. Asynchronous designs require additional considerations, such as handling metastability issues and ensuring proper timing constraints.

Importance of Synchronous Inputs:

Synchronous inputs provide a structured and predictable way to control the operation of digital circuits. By using a clock signal, the circuit can be designed to perform specific actions at specific times. This allows for more reliable and consistent behavior, especially in complex systems where numerous signals need to be coordinated.

In contrast, asynchronous inputs can introduce unpredictable behavior and can be challenging to analyze and debug. They are typically used in specialized cases where specific timing requirements or functionality necessitate their use.

In conclusion, S-R, J-K, and D inputs are called synchronous inputs because they are synchronized with a clock signal and change their state only at specific clock edges. Synchronous inputs provide a structured and predictable way to control the behavior and timing of digital circuits, ensuring reliable and consistent operation.

Master slave flip flop is also referred to as?- a)Level triggered flip flop

- b)Pulse triggered flip flop

- c)Edge triggered flip flop

- d)Edge-Level triggered flip flop

Correct answer is option 'B'. Can you explain this answer?

Master slave flip flop is also referred to as?

a)

Level triggered flip flop

b)

Pulse triggered flip flop

c)

Edge triggered flip flop

d)

Edge-Level triggered flip flop

| | Pooja Patel answered |

The term pulse triggered means the data is entered on the rising edge of the clock pulse, but the output does not reflect the change until the falling edge of the clock pulse.

In which of the following condition the SR flip flop are unstable?- a)S = 0, R = 1

- b)S = 1, R = 0

- c)S = 0, R = 0

- d)S = 1, R = 1

Correct answer is option 'D'. Can you explain this answer?

In which of the following condition the SR flip flop are unstable?

a)

S = 0, R = 1

b)

S = 1, R = 0

c)

S = 0, R = 0

d)

S = 1, R = 1

| | Upasana Joshi answered |

SR Flip Flop Stability

The SR flip flop is a basic type of flip flop that consists of two inputs, S (Set) and R (Reset), and two outputs, Q (Output) and Q' (Inverted Output). It is used to store one bit of information and can be triggered by a clock signal.

Stability of SR Flip Flop

The stability of an SR flip flop refers to its ability to maintain a stable output state when the inputs are changed. In other words, a stable flip flop should not change its output state when the inputs are changed.

Explanation of Options

a) S = 0, R = 1:

In this case, the Set input S is 0 and the Reset input R is 1. When the Set input is 0 and the Reset input is 1, the flip flop enters an unstable state. This is because both inputs are active, which violates the normal operation of the flip flop. The output state becomes unpredictable, and it may toggle between different states or remain in an undefined state.

b) S = 1, R = 0:

In this case, the Set input S is 1 and the Reset input R is 0. When the Set input is 1 and the Reset input is 0, the flip flop enters an unstable state. This is again because both inputs are active, violating the normal operation of the flip flop. The output state becomes unpredictable and may toggle between different states or remain in an undefined state.

c) S = 0, R = 0:

In this case, both the Set input S and the Reset input R are 0. When both inputs are 0, the flip flop remains in its current state. The output state does not change, and the flip flop remains stable.

d) S = 1, R = 1:

In this case, both the Set input S and the Reset input R are 1. When both inputs are 1, the flip flop enters an unstable state. This is because both inputs are active, violating the normal operation of the flip flop. The output state becomes unpredictable and may toggle between different states or remain in an undefined state.

Conclusion

The SR flip flop is unstable when both the Set and Reset inputs are 1 (Option D). In this case, the flip flop enters an unpredictable state, and the output may toggle or remain undefined. Therefore, the correct answer is option D.

The SR flip flop is a basic type of flip flop that consists of two inputs, S (Set) and R (Reset), and two outputs, Q (Output) and Q' (Inverted Output). It is used to store one bit of information and can be triggered by a clock signal.

Stability of SR Flip Flop

The stability of an SR flip flop refers to its ability to maintain a stable output state when the inputs are changed. In other words, a stable flip flop should not change its output state when the inputs are changed.

Explanation of Options

a) S = 0, R = 1:

In this case, the Set input S is 0 and the Reset input R is 1. When the Set input is 0 and the Reset input is 1, the flip flop enters an unstable state. This is because both inputs are active, which violates the normal operation of the flip flop. The output state becomes unpredictable, and it may toggle between different states or remain in an undefined state.

b) S = 1, R = 0:

In this case, the Set input S is 1 and the Reset input R is 0. When the Set input is 1 and the Reset input is 0, the flip flop enters an unstable state. This is again because both inputs are active, violating the normal operation of the flip flop. The output state becomes unpredictable and may toggle between different states or remain in an undefined state.

c) S = 0, R = 0:

In this case, both the Set input S and the Reset input R are 0. When both inputs are 0, the flip flop remains in its current state. The output state does not change, and the flip flop remains stable.

d) S = 1, R = 1:

In this case, both the Set input S and the Reset input R are 1. When both inputs are 1, the flip flop enters an unstable state. This is because both inputs are active, violating the normal operation of the flip flop. The output state becomes unpredictable and may toggle between different states or remain in an undefined state.

Conclusion

The SR flip flop is unstable when both the Set and Reset inputs are 1 (Option D). In this case, the flip flop enters an unpredictable state, and the output may toggle or remain undefined. Therefore, the correct answer is option D.

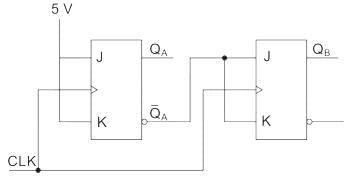

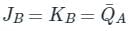

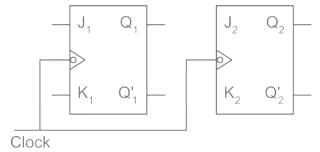

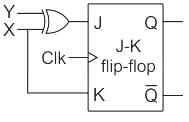

The current state QA QB of a two JK flip-flop system is 00. Assume that the clock rise-time is much smaller than the delay of the JK flip-flop. The next state of the system is.

- a)00

- b)01

- c)11

- d)10

Correct answer is option 'C'. Can you explain this answer?

The current state QA QB of a two JK flip-flop system is 00. Assume that the clock rise-time is much smaller than the delay of the JK flip-flop. The next state of the system is.

a)

00

b)

01

c)

11

d)

10

| | Pooja Patel answered |

In the given circuit

We have,

JA = KA = 1

So next state will be 11

Which of the following is true?- a)A flip-flop and latch both function same

- b)flip-flop is edge triggered and latch is level triggered

- c)Flip-flop is level triggered and latch is edge triggered

- d)Either of flip-flop and latch is a combinational circuit

Correct answer is option 'B'. Can you explain this answer?

Which of the following is true?

a)

A flip-flop and latch both function same

b)

flip-flop is edge triggered and latch is level triggered

c)

Flip-flop is level triggered and latch is edge triggered

d)

Either of flip-flop and latch is a combinational circuit

| | Preethi Banerjee answered |

Flip-Flop and Latch: Differences and Functions

Introduction

Flip-flops and latches are fundamental building blocks in digital circuits, commonly used for storing and transferring data. Although they serve similar purposes, they have distinct differences in terms of triggering mechanism and functionality. This answer aims to explain these differences and highlight the correct option.

Flip-Flop

- A flip-flop is a sequential logic device that stores a single bit of data.

- It has two stable states, typically denoted as "0" and "1."

- The transition between these states occurs on a specific edge of a clock signal.

- The most common types of flip-flops are D flip-flop, JK flip-flop, T flip-flop, and SR flip-flop.

- Flip-flops are commonly used for applications such as data storage, counters, and registers.

- The transition from one state to another in a flip-flop is synchronized with the clock signal, making it edge-triggered.

Latch

- A latch is also a sequential logic device that stores a single bit of data.

- It has two stable states, similar to a flip-flop.

- The transition between these states is controlled by an enable signal.

- Latches are classified into different types, including SR latch, D latch, JK latch, and T latch.

- Latches are commonly used for applications such as data synchronization and data transfer.

- The transition from one state to another in a latch is controlled by the enable signal, making it level-triggered.

Differences

1. Triggering Mechanism:

- Flip-flops are edge-triggered, meaning they change state when a specific edge (rising or falling) of the clock signal occurs.

- Latches are level-triggered, meaning they change state when the enable signal is at a specific level (high or low), regardless of the clock signal.

2. Functionality:

- Flip-flops are primarily used for applications that require synchronization with the clock signal, such as storing data in registers or creating sequential circuits.

- Latches are commonly used for applications that require immediate data transfer or synchronization without the need for a clock signal.

Correct Answer: Option B

The correct option is B because it states that flip-flops are edge-triggered, while latches are level-triggered. This accurately describes the differences between these two sequential logic devices.

Introduction

Flip-flops and latches are fundamental building blocks in digital circuits, commonly used for storing and transferring data. Although they serve similar purposes, they have distinct differences in terms of triggering mechanism and functionality. This answer aims to explain these differences and highlight the correct option.

Flip-Flop

- A flip-flop is a sequential logic device that stores a single bit of data.

- It has two stable states, typically denoted as "0" and "1."

- The transition between these states occurs on a specific edge of a clock signal.

- The most common types of flip-flops are D flip-flop, JK flip-flop, T flip-flop, and SR flip-flop.

- Flip-flops are commonly used for applications such as data storage, counters, and registers.

- The transition from one state to another in a flip-flop is synchronized with the clock signal, making it edge-triggered.

Latch

- A latch is also a sequential logic device that stores a single bit of data.

- It has two stable states, similar to a flip-flop.

- The transition between these states is controlled by an enable signal.

- Latches are classified into different types, including SR latch, D latch, JK latch, and T latch.

- Latches are commonly used for applications such as data synchronization and data transfer.

- The transition from one state to another in a latch is controlled by the enable signal, making it level-triggered.

Differences

1. Triggering Mechanism:

- Flip-flops are edge-triggered, meaning they change state when a specific edge (rising or falling) of the clock signal occurs.

- Latches are level-triggered, meaning they change state when the enable signal is at a specific level (high or low), regardless of the clock signal.

2. Functionality:

- Flip-flops are primarily used for applications that require synchronization with the clock signal, such as storing data in registers or creating sequential circuits.

- Latches are commonly used for applications that require immediate data transfer or synchronization without the need for a clock signal.

Correct Answer: Option B

The correct option is B because it states that flip-flops are edge-triggered, while latches are level-triggered. This accurately describes the differences between these two sequential logic devices.

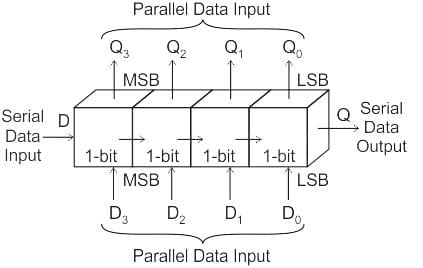

What is meant by the parallel load of a shift register?- a)All FFs are preset with data

- b)Each FF is loaded with data, one at a time

- c)Parallel shifting of data

- d)All FFs are set with data

Correct answer is option 'A'. Can you explain this answer?

What is meant by the parallel load of a shift register?

a)

All FFs are preset with data

b)

Each FF is loaded with data, one at a time

c)

Parallel shifting of data

d)

All FFs are set with data

| | Pooja Patel answered |

At Preset condition, outputs of flip-flops will be 1. Preset = 1 means Q = 1, thus input is definitely 1.

Minimum number of flip flops required for Modulus 15 counter is - a)15

- b)16

- c)4

- d)3

Correct answer is option 'C'. Can you explain this answer?

Minimum number of flip flops required for Modulus 15 counter is

a)

15

b)

16

c)

4

d)

3

| | Madhurima Das answered |

Explanation:

To understand why the minimum number of flip-flops required for a Modulus 15 counter is 4, let's first discuss what a Modulus counter is.

A Modulus counter is a type of counter that counts up to a specific value before resetting back to zero. In this case, we need a counter that counts up to 15 before resetting back to zero.

To determine the minimum number of flip-flops required for a Modulus counter, we can use the formula:

N = ceil(log2(M))

Where N is the number of flip-flops and M is the Modulus value.

Calculating the number of flip-flops:

In this case, the Modulus value is 15. Using the formula, we can calculate the number of flip-flops required as follows:

N = ceil(log2(15))

N = ceil(3.91)

Since the number of flip-flops cannot be a fraction, we need to round up to the nearest whole number. Therefore, N = 4.

Explanation of the formula:

The formula N = ceil(log2(M)) is derived from the fact that each flip-flop can store 2 different states (0 or 1). In a binary counter, the number of different states it can represent is equal to 2^N, where N is the number of flip-flops.

In a Modulus counter, the maximum count value is M. Therefore, the number of different states the counter needs to represent is M + 1 (including zero). In binary, this is represented by log2(M+1).

Since each flip-flop stores 2 different states, we divide log2(M+1) by 2 to determine the number of flip-flops required. Finally, we round up to the nearest whole number using the ceil function.

Conclusion:

In conclusion, the minimum number of flip-flops required for a Modulus 15 counter is 4. This is determined using the formula N = ceil(log2(M)), where M is the Modulus value.

To understand why the minimum number of flip-flops required for a Modulus 15 counter is 4, let's first discuss what a Modulus counter is.

A Modulus counter is a type of counter that counts up to a specific value before resetting back to zero. In this case, we need a counter that counts up to 15 before resetting back to zero.

To determine the minimum number of flip-flops required for a Modulus counter, we can use the formula:

N = ceil(log2(M))

Where N is the number of flip-flops and M is the Modulus value.

Calculating the number of flip-flops:

In this case, the Modulus value is 15. Using the formula, we can calculate the number of flip-flops required as follows:

N = ceil(log2(15))

N = ceil(3.91)

Since the number of flip-flops cannot be a fraction, we need to round up to the nearest whole number. Therefore, N = 4.

Explanation of the formula:

The formula N = ceil(log2(M)) is derived from the fact that each flip-flop can store 2 different states (0 or 1). In a binary counter, the number of different states it can represent is equal to 2^N, where N is the number of flip-flops.

In a Modulus counter, the maximum count value is M. Therefore, the number of different states the counter needs to represent is M + 1 (including zero). In binary, this is represented by log2(M+1).

Since each flip-flop stores 2 different states, we divide log2(M+1) by 2 to determine the number of flip-flops required. Finally, we round up to the nearest whole number using the ceil function.

Conclusion:

In conclusion, the minimum number of flip-flops required for a Modulus 15 counter is 4. This is determined using the formula N = ceil(log2(M)), where M is the Modulus value.

How many types of triggering take place in a flip flops?- a)3

- b)2

- c)4

- d)5

Correct answer is option 'A'. Can you explain this answer?

How many types of triggering take place in a flip flops?

a)

3

b)

2

c)

4

d)

5

| | Rajesh Saha answered |

Types of Triggering in Flip-Flops

Flip-flops are fundamental building blocks in digital electronics, often used for storing binary data. They can be triggered in various ways, which determines how they respond to input signals.

1. Edge Triggering

- This method activates the flip-flop on the transition of the clock signal.

- There are two types of edge triggering:

- Positive Edge Triggering: The flip-flop changes state on the rising edge of the clock pulse.

- Negative Edge Triggering: The flip-flop changes state on the falling edge of the clock pulse.

2. Level Triggering

- In this method, the flip-flop is sensitive to the level of the clock signal rather than its edges.

- The flip-flop remains in an active state as long as the clock signal is at a certain level (high or low).

- This type can lead to issues like glitches, as it may respond to noise on the clock line.

3. Pulse Triggering

- Pulse triggering uses a short pulse to activate the flip-flop.

- The flip-flop captures input data only during the pulse duration, making it less prone to noise compared to level triggering.

- It ensures that the data is stable and valid during the pulse period.

Conclusion

In summary, the three types of triggering in flip-flops are edge triggering, level triggering, and pulse triggering. Each type has its unique characteristics and application scenarios, making them essential for various digital circuit designs. Understanding these triggering methods is crucial for electrical engineers working with sequential circuits.

Flip-flops are fundamental building blocks in digital electronics, often used for storing binary data. They can be triggered in various ways, which determines how they respond to input signals.

1. Edge Triggering

- This method activates the flip-flop on the transition of the clock signal.

- There are two types of edge triggering:

- Positive Edge Triggering: The flip-flop changes state on the rising edge of the clock pulse.

- Negative Edge Triggering: The flip-flop changes state on the falling edge of the clock pulse.

2. Level Triggering

- In this method, the flip-flop is sensitive to the level of the clock signal rather than its edges.

- The flip-flop remains in an active state as long as the clock signal is at a certain level (high or low).

- This type can lead to issues like glitches, as it may respond to noise on the clock line.

3. Pulse Triggering

- Pulse triggering uses a short pulse to activate the flip-flop.

- The flip-flop captures input data only during the pulse duration, making it less prone to noise compared to level triggering.

- It ensures that the data is stable and valid during the pulse period.

Conclusion

In summary, the three types of triggering in flip-flops are edge triggering, level triggering, and pulse triggering. Each type has its unique characteristics and application scenarios, making them essential for various digital circuit designs. Understanding these triggering methods is crucial for electrical engineers working with sequential circuits.

The terminal count of a typical modulus-10 binary counter is ____________- a)0000

- b)1010

- c)1001

- d)1111

Correct answer is option 'C'. Can you explain this answer?

The terminal count of a typical modulus-10 binary counter is ____________

a)

0000

b)

1010

c)

1001

d)

1111

| | Mahi Bose answered |

The terminal count of a typical modulus-10 binary counter is 1001 (option C). This means that when the counter reaches its maximum count value, it will output the binary number 1001.

To understand why option C is the correct answer, let's break down the operation of a modulus-10 binary counter.

Modulus-10 Binary Counter:

A binary counter is a sequential circuit that cycles through a predefined sequence of binary values. The modulus-10 binary counter is designed to count from 0 to 9 and repeat. It uses four flip-flops to store the binary values.

Binary Representation:

In a binary system, each digit can have two possible states: 0 or 1. To represent the numbers from 0 to 9, we require four binary digits.

The binary representation of the numbers from 0 to 9 are:

0 - 0000

1 - 0001

2 - 0010

3 - 0011

4 - 0100

5 - 0101

6 - 0110

7 - 0111

8 - 1000

9 - 1001

Terminal Count:

The terminal count refers to the maximum count value that the counter can reach before it resets to zero and starts counting again. In the case of a modulus-10 binary counter, the terminal count is 9, which is represented in binary as 1001.

Explanation of Option C:

Option C, which is 1001, represents the binary equivalent of the terminal count of a modulus-10 binary counter. When the counter reaches its maximum count of 9, it will output the binary number 1001.

Therefore, option C (1001) is the correct answer for the terminal count of a typical modulus-10 binary counter.

In summary:

- A modulus-10 binary counter counts from 0 to 9 and repeats.

- The terminal count is the maximum count value before the counter resets.

- The binary representation of the terminal count is 1001 (option C).

To understand why option C is the correct answer, let's break down the operation of a modulus-10 binary counter.

Modulus-10 Binary Counter:

A binary counter is a sequential circuit that cycles through a predefined sequence of binary values. The modulus-10 binary counter is designed to count from 0 to 9 and repeat. It uses four flip-flops to store the binary values.

Binary Representation:

In a binary system, each digit can have two possible states: 0 or 1. To represent the numbers from 0 to 9, we require four binary digits.

The binary representation of the numbers from 0 to 9 are:

0 - 0000

1 - 0001

2 - 0010

3 - 0011

4 - 0100

5 - 0101

6 - 0110

7 - 0111

8 - 1000

9 - 1001

Terminal Count:

The terminal count refers to the maximum count value that the counter can reach before it resets to zero and starts counting again. In the case of a modulus-10 binary counter, the terminal count is 9, which is represented in binary as 1001.

Explanation of Option C:

Option C, which is 1001, represents the binary equivalent of the terminal count of a modulus-10 binary counter. When the counter reaches its maximum count of 9, it will output the binary number 1001.

Therefore, option C (1001) is the correct answer for the terminal count of a typical modulus-10 binary counter.

In summary:

- A modulus-10 binary counter counts from 0 to 9 and repeats.

- The terminal count is the maximum count value before the counter resets.

- The binary representation of the terminal count is 1001 (option C).

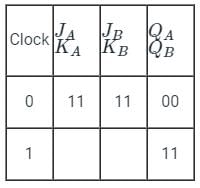

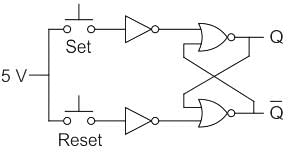

An SR latch is implemented using TTL gates as shown in the figure. The set and reset pulse inputs are provided using the push-button switches. It is observed that the circuit fails to work as desired. The SR latch can be made functional by changing

- a)NOR gates to NAND gates

- b)inverters to buffers

- c)NOR gates to NAND gates and inverters to buffers

- d)5 V to ground

Correct answer is option 'D'. Can you explain this answer?

An SR latch is implemented using TTL gates as shown in the figure. The set and reset pulse inputs are provided using the push-button switches. It is observed that the circuit fails to work as desired. The SR latch can be made functional by changing

a)

NOR gates to NAND gates

b)

inverters to buffers

c)

NOR gates to NAND gates and inverters to buffers

d)

5 V to ground

| Cstoppers Instructors answered |

Concept:

- In the TTL logic gate, open-end or floating end are considered as logic-1.

- For the circuit to work as an S & R latch, S & R should act as logic-0 as well as logic- 1 on requirement.

Analysis:

- If we connect set which is equal to 5 volts, then it will be considered as logic-1.

- If we do not connect 5 Volts to set switch i.e. if we make set switch ‘open’ then it will again be considered as a logic -1, because it is a TTL gate.

- So we have to replace 5 V supply with 0 Volts by connecting it to ground. So logic-0 is also possible for switch ‘set’ & ‘reset’.

Hence for the above circuit to work as an SR latch, 5-volt battery should connect to ground.

Hence option -4 is Correct.

The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)

Correct answer is between '12.3,12.7'. Can you explain this answer?

The maximum clock frequency in MHz of a 4-stage ripple counter, utilizing flip-flops, with each flip-flop having a propagation delay of 20 ns, is ___________. (round off to one decimal place)

| | Pooja Patel answered |

Concept:

For the n-stage ripple counter, the no. of flip-flops used are n.

If Each flip flop is having propagation delay of tp seconds.

Then overall propagation delay of the n-stage ripple counter is 'ntp'

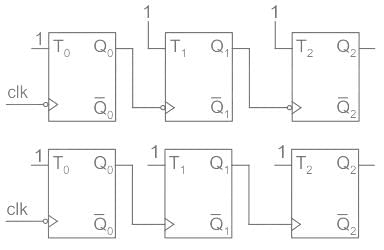

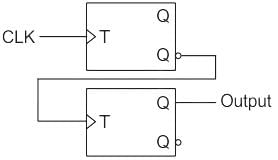

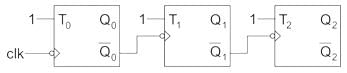

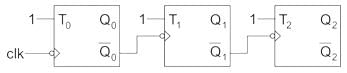

Both of the above diagrams is a 3 stage up counter.

i.e., 3 flip-flops are used.

In order to obtain Q2, the 3 clocks will be used at a different instant or at the instant when each flip flop will get their input.

If each flip flop is having 'tp' as propagation delay, then to get output, the overall propagation Delay will be sum of the propagation Delay of each flip flop.

Explanation:

Given

Ripple counter 4 flip flop

tp = 20 n second for each flip flop.

T = n tp = total propagation delay

⇒ T = 4 × 20 n sec = 80 n sec

Clock frequency =

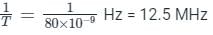

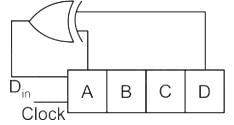

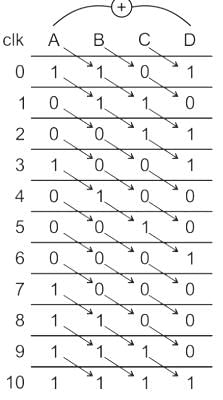

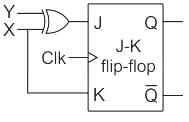

A 4-bit shift register circuit configured for right-shift operation, i.e. Din → A, A → B, B → C, C → D, is shown. If the present state of the shift register is ABCD = 1101, the number of clock cycles required to reach the state ABCD = 1111 is ________.

Correct answer is '10'. Can you explain this answer?

A 4-bit shift register circuit configured for right-shift operation, i.e. Din → A, A → B, B → C, C → D, is shown. If the present state of the shift register is ABCD = 1101, the number of clock cycles required to reach the state ABCD = 1111 is ________.

| Cstoppers Instructors answered |

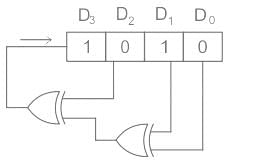

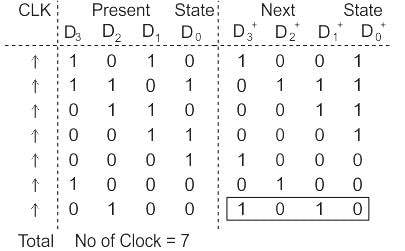

Input to A is Exor of Previous value of A and D

New Input to B , C, D are previous values of A, B, C respectively.

Total clock cycles required is 10

How many different states does a 3-bit asynchronous counter have?- a)2

- b)4

- c)8

- d)16

Correct answer is option 'C'. Can you explain this answer?

How many different states does a 3-bit asynchronous counter have?

a)

2

b)

4

c)

8

d)

16

| | Mainak Pillai answered |

Solution:

A 3-bit asynchronous counter is a digital circuit that counts from 0 to 7 in binary. Each flip-flop in the counter represents one bit, and the number of possible states is determined by the number of bits.

To determine the number of different states, we need to consider the binary representation of each state.

- In a 3-bit counter, the binary representation of the states ranges from 000 to 111.

- The first bit can take on two values: 0 or 1.

- The second bit can also take on two values: 0 or 1.

- The third bit can also take on two values: 0 or 1.

Hence, to find the total number of states, we multiply the number of choices for each bit:

2 * 2 * 2 = 8

Therefore, a 3-bit asynchronous counter has 8 different states.

Therefore, the correct answer is option 'C' (8).

A 3-bit asynchronous counter is a digital circuit that counts from 0 to 7 in binary. Each flip-flop in the counter represents one bit, and the number of possible states is determined by the number of bits.

To determine the number of different states, we need to consider the binary representation of each state.

- In a 3-bit counter, the binary representation of the states ranges from 000 to 111.

- The first bit can take on two values: 0 or 1.

- The second bit can also take on two values: 0 or 1.

- The third bit can also take on two values: 0 or 1.

Hence, to find the total number of states, we multiply the number of choices for each bit:

2 * 2 * 2 = 8

Therefore, a 3-bit asynchronous counter has 8 different states.

Therefore, the correct answer is option 'C' (8).

The outputs of SR latch are ___________- a)x and y

- b)a and b

- c)s and r

- d)q and q’

Correct answer is option 'D'. Can you explain this answer?

The outputs of SR latch are ___________

a)

x and y

b)

a and b

c)

s and r

d)

q and q’

| | Pooja Patel answered |

SR or Set-Reset latch is the simplest type of bistable multivibrator having two stable states. The inputs of SR latch are s and r while outputs are q and q’. It is clear from the diagram:

.

.

.

.The asynchronous input can be used to set the flip-flop to the ____________- a)1 state

- b)0 state

- c)either 1 or 0 state

- d)forbidden State

Correct answer is option 'C'. Can you explain this answer?

The asynchronous input can be used to set the flip-flop to the ____________

a)

1 state

b)

0 state

c)

either 1 or 0 state

d)

forbidden State

| | Pooja Patel answered |

The asynchronous input can be used to set the flip-flop to the 1 state or clear the flip-flop to the 0 state at any time, regardless of the condition at the other inputs.

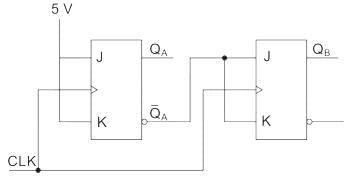

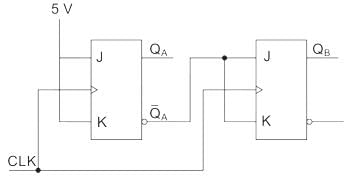

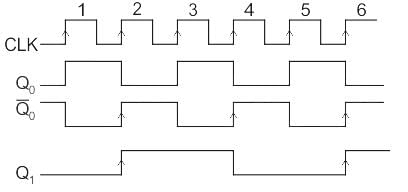

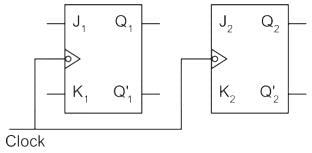

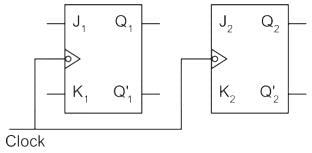

Determine the output frequency of the given circuit if the input CLK frequency is 1 MHz.

- a)0.5 MHz

- b)250 kHz

- c)4 MHz

- d)1 KHz

Correct answer is option 'B'. Can you explain this answer?

Determine the output frequency of the given circuit if the input CLK frequency is 1 MHz.

a)

0.5 MHz

b)

250 kHz

c)

4 MHz

d)

1 KHz

| | Pooja Patel answered |

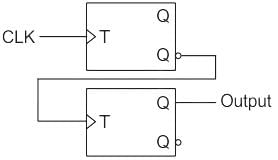

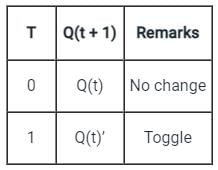

Concept:

T flip-flop

The truth table of the T flip-flop is given by:

The characteristic table of the T flip-flop is:

The characteristic equation of the T flip-flop is:

Q(t + 1) = T ⊕ Q(t)

Analysis:

From the given circuit two flip-flops are present and the Q1’ output is connected to the input of the second flip-flop.

T2 = Q1’

Given circuit is an example of the Down counter.

The below figure represents the waveforms for the respective clock edges.

The flip-flop2 will trigger only when the Q1’ is going from 0 to 1, i.e., positive triggering of the Q1’.

In the output is Q1 the total time period is 4 times that of the clock (4T).

Conclusion:

As the time period is 4 times then the frequency will be divided by four times.

fout = 0.25 MHz = 250 kHz

The S-R latch is an example of:- a)Combinational circuit

- b)Synchronous sequential circuit

- c)One-bit memory element

- d)One-clock delay element

Correct answer is option 'C'. Can you explain this answer?

The S-R latch is an example of:

a)

Combinational circuit

b)

Synchronous sequential circuit

c)

One-bit memory element

d)

One-clock delay element

| | Rajesh Saha answered |

One-Bit Memory Element - S-R Latch

The S-R latch is a sequential logic circuit that is used as a one-bit memory element. It has two inputs, Set (S) and Reset (R), and two outputs, Q and Q'. The output Q represents the stored value of the latch, and Q' represents the complement of Q.

How it works

When the S input is high and R input is low, the Q output goes high, and Q' output goes low. This state is called SET. Conversely, when the R input is high and the S input is low, the Q output goes low, and Q' output goes high. This state is called RESET.

When both S and R inputs are low, the output state of the latch remains unchanged from its previous state, making it a memory element.

Applications

The S-R latch is used in various applications such as:

1. As a memory element in flip-flops and registers.

2. As a building block in more complex sequential circuits.

3. As a basic element in control circuits for digital systems.

Conclusion

In conclusion, the S-R latch is an example of a one-bit memory element. It is a simple and widely used digital circuit element that stores one binary bit of information.

The S-R latch is a sequential logic circuit that is used as a one-bit memory element. It has two inputs, Set (S) and Reset (R), and two outputs, Q and Q'. The output Q represents the stored value of the latch, and Q' represents the complement of Q.

How it works

When the S input is high and R input is low, the Q output goes high, and Q' output goes low. This state is called SET. Conversely, when the R input is high and the S input is low, the Q output goes low, and Q' output goes high. This state is called RESET.

When both S and R inputs are low, the output state of the latch remains unchanged from its previous state, making it a memory element.

Applications

The S-R latch is used in various applications such as:

1. As a memory element in flip-flops and registers.

2. As a building block in more complex sequential circuits.

3. As a basic element in control circuits for digital systems.

Conclusion

In conclusion, the S-R latch is an example of a one-bit memory element. It is a simple and widely used digital circuit element that stores one binary bit of information.

The characteristic equation of D-flip-flop implies that ___________- a)The next state is dependent on previous state

- b)The next state is dependent on present state

- c)The next state is independent of previous state

- d)The next state is independent of present state

Correct answer is option 'D'. Can you explain this answer?

The characteristic equation of D-flip-flop implies that ___________

a)

The next state is dependent on previous state

b)

The next state is dependent on present state

c)

The next state is independent of previous state

d)

The next state is independent of present state

| | Pooja Patel answered |

A characteristic equation is needed when a specific gate requires a specific output in order to satisfy the truth table. The characteristic equation of D flip-flop is given by Q(n+1) = D; which indicates that the next state is independent of the present state.

Four J-K flip-flops are cascaded with their J-K inputs tied HIGH. If the input frequency (fin) to the first flip-flop is 32 kHz, the output frequency (fout) is ________- a)1 kHz

- b)2 kHz

- c)4 kHz

- d)16 kHz

Correct answer is option 'B'. Can you explain this answer?

Four J-K flip-flops are cascaded with their J-K inputs tied HIGH. If the input frequency (fin) to the first flip-flop is 32 kHz, the output frequency (fout) is ________

a)

1 kHz

b)

2 kHz

c)

4 kHz

d)

16 kHz

| | Pooja Patel answered |

32/2 = 16:-first flip-flop,

16/2 = 8:- second flip-flop,

8/2 = 4:- third flip-flop,

4/2 = 2:- fourth flip-flop.

Since the output frequency is determined on basis of the 4th flip-flop.

16/2 = 8:- second flip-flop,

8/2 = 4:- third flip-flop,

4/2 = 2:- fourth flip-flop.

Since the output frequency is determined on basis of the 4th flip-flop.

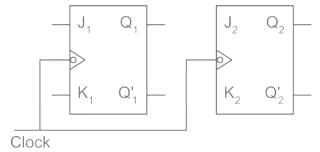

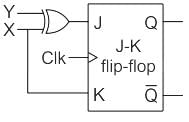

A synchronous counter using two J – K flip flops that goes through the sequence of states: Q1 Q2 = 00 → 10 → 01 → 11 → 00 …. is required. To achieve this, the inputs to the flip flops are

- a)J1 = Q2, K1 = 0; J2 = Q1’, K2 = Q1

- b)J1 = 1, K1 = 1; J2 = Q1, K2 = Q1

- c)J1 = Q2, K1 = Q2’; J2 = 1, K2 = 1

- d)J1 = Q2’, K1 = Q2; J2 = Q1, K2 = Q1’

Correct answer is option 'B'. Can you explain this answer?

A synchronous counter using two J – K flip flops that goes through the sequence of states: Q1 Q2 = 00 → 10 → 01 → 11 → 00 …. is required. To achieve this, the inputs to the flip flops are

a)

J1 = Q2, K1 = 0; J2 = Q1’, K2 = Q1

b)

J1 = 1, K1 = 1; J2 = Q1, K2 = Q1

c)

J1 = Q2, K1 = Q2’; J2 = 1, K2 = 1

d)

J1 = Q2’, K1 = Q2; J2 = Q1, K2 = Q1’

| | Pooja Patel answered |

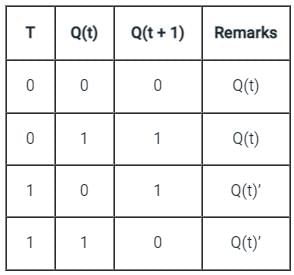

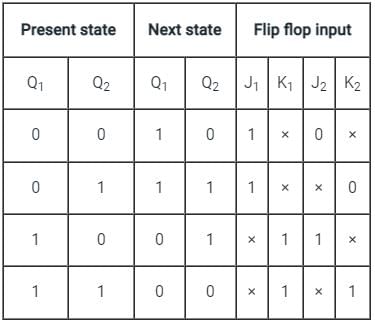

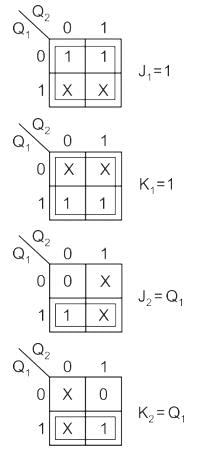

By using excitation table of JK flip flop.

From the above table,

A D flip-flop utilizing a PGT clock is in the CLEAR state. Which of the following input actions will cause it to change states?- a)CLK = NGT, D = 0

- b)CLK = PGT, D = 0

- c)CLOCK NGT, D = 1

- d)CLOCK PGT, D = 1

Correct answer is option 'D'. Can you explain this answer?

A D flip-flop utilizing a PGT clock is in the CLEAR state. Which of the following input actions will cause it to change states?

a)

CLK = NGT, D = 0

b)

CLK = PGT, D = 0

c)

CLOCK NGT, D = 1

d)

CLOCK PGT, D = 1

| | Pooja Patel answered |

PGT refers to Positive Going Transition and NGT refers to negative Going Transition. Earlier, the DFF is in a clear state (output is 0). So, if D = 1 then in the next stage output will be 1 and hence the stage will be changed.

The number of J-K flip flops in modulo 16 binary up-counter are:- a)16

- b)4

- c)8

- d)2

Correct answer is option 'B'. Can you explain this answer?

The number of J-K flip flops in modulo 16 binary up-counter are:

a)

16

b)

4

c)

8

d)

2

| | Pooja Patel answered |

Calculation:

For a Modulo-N counter, which can count to a total of N-states, the number of flip-flops required is:

N ≥ 2n

Govem N = 16

So, 16 = 2n

n = 4

So, the number of J-K flip-flops in Modulo-16 binary up-counter is 4.

A D flip-flop can be constructed from an ______ flip-flop.- a)S-R

- b)J-K

- c)T

- d)S-K

Correct answer is option 'A'. Can you explain this answer?

A D flip-flop can be constructed from an ______ flip-flop.

a)

S-R

b)

J-K

c)

T

d)

S-K

| Mihir Kulkarni answered |

A D flip-flop can be constructed from an S-R flip-flop.

Explanation:

To understand why a D flip-flop can be constructed from an S-R flip-flop, let's first understand the basic working of both flip-flops.

S-R Flip-Flop:

An S-R (Set-Reset) flip-flop is a basic flip-flop that has two inputs, S (Set) and R (Reset), and two outputs, Q (output) and Q' (complement of output). It operates based on the logic levels of the inputs as follows:

- When S = 1 and R = 0, the flip-flop sets and Q = 1.

- When S = 0 and R = 1, the flip-flop resets and Q = 0.

- When both S and R are 0 or both S and R are 1, the flip-flop holds its previous state.

D Flip-Flop:

A D flip-flop, also known as a data flip-flop, has a single input, D (data), and two outputs, Q and Q'. It operates based on the logic level of the input as follows:

- When D = 1, the flip-flop stores the value 1 and Q = 1.

- When D = 0, the flip-flop stores the value 0 and Q = 0.

Construction of D Flip-Flop from S-R Flip-Flop:

A D flip-flop can be constructed from an S-R flip-flop by connecting the inputs of the S-R flip-flop in a specific way. Here's how it can be done:

1. Connect the D input of the D flip-flop to both the Set (S) and Reset (R) inputs of the S-R flip-flop.

- This ensures that the S-R flip-flop behaves like a D flip-flop.

2. Connect the complement of the Q output of the S-R flip-flop to its Reset (R) input.

- This ensures that the S-R flip-flop resets when Q' = 1, which is the complement of the Q output of the D flip-flop.

3. Connect the Q output of the S-R flip-flop to the input of an inverter.

- This inverter generates the complement of the Q output of the S-R flip-flop, which becomes the Q' output of the D flip-flop.

By following these connections, we effectively convert the S-R flip-flop into a D flip-flop. The S-R flip-flop now behaves exactly like a D flip-flop, where the input D controls the state of the flip-flop and the outputs Q and Q' represent the stored value and its complement, respectively.

Explanation:

To understand why a D flip-flop can be constructed from an S-R flip-flop, let's first understand the basic working of both flip-flops.

S-R Flip-Flop:

An S-R (Set-Reset) flip-flop is a basic flip-flop that has two inputs, S (Set) and R (Reset), and two outputs, Q (output) and Q' (complement of output). It operates based on the logic levels of the inputs as follows:

- When S = 1 and R = 0, the flip-flop sets and Q = 1.

- When S = 0 and R = 1, the flip-flop resets and Q = 0.

- When both S and R are 0 or both S and R are 1, the flip-flop holds its previous state.

D Flip-Flop:

A D flip-flop, also known as a data flip-flop, has a single input, D (data), and two outputs, Q and Q'. It operates based on the logic level of the input as follows:

- When D = 1, the flip-flop stores the value 1 and Q = 1.

- When D = 0, the flip-flop stores the value 0 and Q = 0.

Construction of D Flip-Flop from S-R Flip-Flop:

A D flip-flop can be constructed from an S-R flip-flop by connecting the inputs of the S-R flip-flop in a specific way. Here's how it can be done:

1. Connect the D input of the D flip-flop to both the Set (S) and Reset (R) inputs of the S-R flip-flop.

- This ensures that the S-R flip-flop behaves like a D flip-flop.

2. Connect the complement of the Q output of the S-R flip-flop to its Reset (R) input.

- This ensures that the S-R flip-flop resets when Q' = 1, which is the complement of the Q output of the D flip-flop.

3. Connect the Q output of the S-R flip-flop to the input of an inverter.

- This inverter generates the complement of the Q output of the S-R flip-flop, which becomes the Q' output of the D flip-flop.

By following these connections, we effectively convert the S-R flip-flop into a D flip-flop. The S-R flip-flop now behaves exactly like a D flip-flop, where the input D controls the state of the flip-flop and the outputs Q and Q' represent the stored value and its complement, respectively.

If the counter has 3 flip-flops, then the maximum binary number that it counts is equal to:- a)101

- b)011

- c)111

- d)110

Correct answer is option 'C'. Can you explain this answer?

If the counter has 3 flip-flops, then the maximum binary number that it counts is equal to:

a)

101

b)

011

c)

111

d)

110

| | Pooja Patel answered |

Concept:

The maximum no. of states that can be represented by N flip-flops is given by:

No. of states = 2N

Calculation:

Given, N = 3

No. of states = 23 = 8

The states from 0 to 7 are represented by 3 flip-flops.

The maximum binary number is 111

Internal propagation delay of asynchronous counter is removed by ____________- a)Ripple counter

- b)Ring counter

- c)Modulus counter

- d)Synchronous counter

Correct answer is option 'D'. Can you explain this answer?

Internal propagation delay of asynchronous counter is removed by ____________

a)

Ripple counter

b)

Ring counter

c)

Modulus counter

d)

Synchronous counter

| | Pooja Patel answered |

Propagation delay refers to the amount of time taken in producing an output when the input is altered. Internal propagation delay of asynchronous counter is removed by synchronous counter because clock input is given to each flip-flop individually in synchronous counter.

When both inputs of SR latches are low, the latch ___________- a)Q output goes high

- b)Q’ output goes high

- c)It remains in its previously set or reset state

- d)it goes to its next set or reset state

Correct answer is option 'C'. Can you explain this answer?

When both inputs of SR latches are low, the latch ___________

a)

Q output goes high

b)

Q’ output goes high

c)

It remains in its previously set or reset state

d)

it goes to its next set or reset state

| | Pooja Patel answered |

When both inputs of SR latches are low, the latch remains in it’s present state. There is no change in output.

An 8-bit ripple counter and an 8 bit synchronous counter are made using flip flops having a propagation delay of 10 ns each. If the worst-case delay in the ripple counter and the synchronous counter be R and S respectively, then - a)R = 10 ns, S = 80 ns

- b)R = 40 ns, S = 10 ns

- c)R = 10 ns, S = 10 ns

- d)R = 80 ns, S = 10 ns

Correct answer is option 'D'. Can you explain this answer?

An 8-bit ripple counter and an 8 bit synchronous counter are made using flip flops having a propagation delay of 10 ns each. If the worst-case delay in the ripple counter and the synchronous counter be R and S respectively, then

a)

R = 10 ns, S = 80 ns

b)

R = 40 ns, S = 10 ns

c)

R = 10 ns, S = 10 ns

d)

R = 80 ns, S = 10 ns

| | Pooja Patel answered |

Concept:

For an n-bit ripple counter, the MSB is generated only when the carry form all the pervious flip-flip are propagated to the MSB flip flop.

So, the maximum time(Worst-Case delay) taken for the output of the Ripple counter to be stable = n × td (where td is the propagation delay of each flip flop)

But in an n-bit synchronous counter, the time taken for the output to be stable is simply the propagation delay of 1 flip-flop i.e. td

Calculation:

Given n = 8 bit and td = 10 ns.

For Ripple counter, the worst-case delay = n × tb = 8 × 10 ns = 80 nsec.

For Synchronous-Counter the worst-case delay is td only, which is 10 ns.

Maximum count value of a n bit counter is- a)2n -1

- b)2n

- c)22n

- d)2n + 1

Correct answer is option 'A'. Can you explain this answer?

Maximum count value of a n bit counter is

a)

2n -1

b)

2n

c)

22n

d)

2n + 1

| | Disha Das answered |

Maximum count value of an n-bit counter

The maximum count value of an n-bit counter refers to the maximum number of distinct states that the counter can represent. In other words, it represents the highest decimal value that can be stored in the counter.

Explanation:

To understand why the maximum count value is 2^n - 1, let's consider a binary counter with n bits. Each bit in the counter can have two possible states: 0 or 1. Therefore, the total number of distinct states that the counter can represent is equal to 2^n.

However, in a binary counter, the counting sequence starts from 0 and goes up to the maximum count value, and then wraps around back to 0. This means that the counter cannot represent the total number of distinct states, as the last state (2^n) is not included.

For example, let's consider a 3-bit counter. The possible states are:

000 (0 in decimal)

001 (1 in decimal)

010 (2 in decimal)

011 (3 in decimal)

100 (4 in decimal)

101 (5 in decimal)

110 (6 in decimal)

111 (7 in decimal)

As you can see, the maximum count value is 7, which is 2^3 - 1. The counter cannot represent the state 2^3 (8 in decimal) because it wraps around back to 0.

Formula:

The formula to calculate the maximum count value of an n-bit counter is given by:

Maximum count value = 2^n - 1

where:

- n is the number of bits in the counter.

Conclusion:

In conclusion, the maximum count value of an n-bit counter is given by the formula 2^n - 1. This formula takes into account the total number of distinct states that the counter can represent, excluding the wrap-around state. It is important to consider the maximum count value when designing and using counters to ensure that the counter does not overflow and that the desired counting range is achieved.

The maximum count value of an n-bit counter refers to the maximum number of distinct states that the counter can represent. In other words, it represents the highest decimal value that can be stored in the counter.

Explanation:

To understand why the maximum count value is 2^n - 1, let's consider a binary counter with n bits. Each bit in the counter can have two possible states: 0 or 1. Therefore, the total number of distinct states that the counter can represent is equal to 2^n.

However, in a binary counter, the counting sequence starts from 0 and goes up to the maximum count value, and then wraps around back to 0. This means that the counter cannot represent the total number of distinct states, as the last state (2^n) is not included.

For example, let's consider a 3-bit counter. The possible states are:

000 (0 in decimal)

001 (1 in decimal)

010 (2 in decimal)

011 (3 in decimal)

100 (4 in decimal)

101 (5 in decimal)

110 (6 in decimal)

111 (7 in decimal)

As you can see, the maximum count value is 7, which is 2^3 - 1. The counter cannot represent the state 2^3 (8 in decimal) because it wraps around back to 0.

Formula:

The formula to calculate the maximum count value of an n-bit counter is given by:

Maximum count value = 2^n - 1

where:

- n is the number of bits in the counter.

Conclusion:

In conclusion, the maximum count value of an n-bit counter is given by the formula 2^n - 1. This formula takes into account the total number of distinct states that the counter can represent, excluding the wrap-around state. It is important to consider the maximum count value when designing and using counters to ensure that the counter does not overflow and that the desired counting range is achieved.

In S-R latch, when the SET input is made high, output Q becomes:- a)0

- b)1

- c)no change

- d)application not allowed

Correct answer is option 'B'. Can you explain this answer?

In S-R latch, when the SET input is made high, output Q becomes:

a)

0

b)

1

c)

no change

d)

application not allowed

| | Naveen Kapoor answered |

Effect of SET input in S-R latch:

When the SET input of an S-R latch is made high, it sets the latch, causing the Q output to become high.

Explanation:

- When the SET input is activated, it overrides the RESET input and forces the Q output to be high.

- This behavior is due to the internal logic of the S-R latch, where the SET input triggers the latch to store a high output.

- The Q output will remain high until a reset signal is applied to the latch.

Conclusion:

In summary, when the SET input of an S-R latch is made high, the output Q will be set to a high state, which can be represented as logic level 1.

When the SET input of an S-R latch is made high, it sets the latch, causing the Q output to become high.

Explanation:

- When the SET input is activated, it overrides the RESET input and forces the Q output to be high.

- This behavior is due to the internal logic of the S-R latch, where the SET input triggers the latch to store a high output.

- The Q output will remain high until a reset signal is applied to the latch.

Conclusion:

In summary, when the SET input of an S-R latch is made high, the output Q will be set to a high state, which can be represented as logic level 1.

The main difference between a register and a counter is ___________- a)A register has no specific sequence of states

- b)A counter has no specific sequence of states

- c)A register has capability to store one bit of information but counter has n-bit

- d)A register counts data

Correct answer is option 'A'. Can you explain this answer?

The main difference between a register and a counter is ___________

a)

A register has no specific sequence of states

b)

A counter has no specific sequence of states

c)

A register has capability to store one bit of information but counter has n-bit

d)

A register counts data

| | Pooja Patel answered |

The main difference between a register and a counter is that a register has no specific sequence of states except in certain specialised applications.

The circuits of NOR based S-R latch classified as asynchronous sequential circuits, why?- a)Because of inverted outputs

- b)Because of triggering functionality

- c)Because of cross-coupled connection

- d)Because of inverted outputs & triggering functionality

Correct answer is option 'C'. Can you explain this answer?

The circuits of NOR based S-R latch classified as asynchronous sequential circuits, why?

a)

Because of inverted outputs

b)

Because of triggering functionality

c)

Because of cross-coupled connection

d)

Because of inverted outputs & triggering functionality

| | Pooja Patel answered |

The cross-coupled connections from the output of one gate to the input of the other gate constitute a feedback path. For this reason, the circuits of NOR based S-R latch classified as asynchronous sequential circuits. Moreover, they are referred to as asynchronous because they function in the absence of a clock pulse.

The term synchronous means ____________- a)The output changes state only when any of the input is triggered

- b)The output changes state only when the clock input is triggered

- c)The output changes state only when the input is reversed

- d)The output changes state only when the input follows it

Correct answer is option 'B'. Can you explain this answer?

The term synchronous means ____________

a)

The output changes state only when any of the input is triggered

b)

The output changes state only when the clock input is triggered

c)

The output changes state only when the input is reversed

d)

The output changes state only when the input follows it

| | Pooja Patel answered |

The term synchronous means the output changes state only when the clock input is triggered. That is, changes in the output occur in synchronization with the clock.

In D register, ‘D’ stands for ___________- a)Delay

- b)Decrement

- c)Data

- d)Decay

Correct answer is option 'C'. Can you explain this answer?

In D register, ‘D’ stands for ___________

a)

Delay

b)

Decrement

c)

Data

d)

Decay

| | Pooja Patel answered |

D stands for “data” in case of flip-flops and not delay. Registers are made of a group of flip-flops.

In D flip-flop, if clock input is HIGH & D=1, then output is ___________- a)0

- b)1

- c)Forbidden

- d)Toggle

Correct answer is option 'A'. Can you explain this answer?

In D flip-flop, if clock input is HIGH & D=1, then output is ___________

a)

0

b)

1

c)

Forbidden

d)

Toggle

| | Swati Shah answered |

And D input is also HIGH, the output of the flip-flop will be HIGH. If the clock input is LOW, the output of the flip-flop will remain unchanged regardless of the input D.

Which of the following statements is not correct about a universal shift register?- a)Universal shift register is a bidirectional register whose inputs can be either in serial form or in parallel form

- b)Universal shift register generates an internal clock to synchronize the operations

- c)We need ‘N’ number of D flipflops and ‘N’ number of MUX to design N-bit universal shift register

- d)The universal shift register has a clear control that clears the contents of the register to 0

Correct answer is option 'B'. Can you explain this answer?

Which of the following statements is not correct about a universal shift register?

a)

Universal shift register is a bidirectional register whose inputs can be either in serial form or in parallel form

b)

Universal shift register generates an internal clock to synchronize the operations

c)

We need ‘N’ number of D flipflops and ‘N’ number of MUX to design N-bit universal shift register

d)

The universal shift register has a clear control that clears the contents of the register to 0

| | Pooja Patel answered |

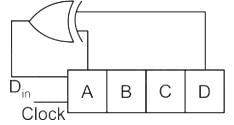

Shift Register:

1). A shift register has the capability to store one bit and if another bit is to store, in such a situation it deletes the previous data and stores them.

2). A universal shift register is a bidirectional register whose inputs can be either in serial form or in parallel form. (Option 1 is true)

3). An n-bit shift register consists of ‘N’ number of D flipflops and ‘N’ number of MUX.(Option 3 is correct)

4). The universal shift register has a clear control that clears the contents of the register to 0 and a preset control to set the contents of the register to 1. (Option 4 is correct)

5). The universal shift register does not have an internal clock to synchronize the operations (Option 2 is false)

The basic block diagram of a shift register is as shown:

A ripple counter’s speed is limited by the propagation delay of ____________- a)Each flip-flop

- b)All flip-flops and gates

- c)The flip-flops only with gates

- d)Only circuit gates

Correct answer is option 'A'. Can you explain this answer?

A ripple counter’s speed is limited by the propagation delay of ____________

a)

Each flip-flop

b)

All flip-flops and gates

c)

The flip-flops only with gates

d)

Only circuit gates

| | Pooja Patel answered |

A ripple counter is something that is derived by other flip-flops. Its like a series of Flip Flops. Output of one FF becomes the input of the next. Because ripple counter is composed of FF only and no gates are there other than FF, so only propagation delay of FF will be taken into account. Propagation delay refers to the amount of time taken in producing an output when the input is altered.

The basic latch consists of ___________- a)Two inverters

- b)Two comparators

- c)Two amplifiers

- d)Two adders

Correct answer is option 'A'. Can you explain this answer?

The basic latch consists of ___________

a)

Two inverters

b)

Two comparators

c)

Two amplifiers

d)

Two adders

| | Pooja Patel answered |

The basic latch consists of two inverters. It is in the sense that if the output Q = 0 then the second output Q’ = 1 and vice versa.

The number of T flip-flops required to realise a mod-10 asynchronous counter is:- a)10

- b)3

- c)4

- d)5

Correct answer is option 'C'. Can you explain this answer?

The number of T flip-flops required to realise a mod-10 asynchronous counter is:

a)

10

b)

3

c)

4

d)

5

| | Pooja Patel answered |

Concept:

For the MOD-N asynchronous counter, the number of T flip-flops is given by:

MOD-N ≼ 2N

where N = No. of flip-flops

Calculation:

MOD 10 ≼ 2N

N = 4

Therefore, the number of T flip-flops required to realize a mod-10 asynchronous counter is 4.

Which of the following describes the operation of a positive edge-triggered D flip-flop?- a)If both inputs are HIGH, the output will toggle

- b)The output will follow the input on the leading edge of the clock

- c)When both inputs are LOW, an invalid state exists

- d)The input is toggled into the flip-flop on the leading edge of the clock and is passed to the output on the trailing edge of the clock

Correct answer is option 'B'. Can you explain this answer?

Which of the following describes the operation of a positive edge-triggered D flip-flop?

a)

If both inputs are HIGH, the output will toggle

b)

The output will follow the input on the leading edge of the clock

c)

When both inputs are LOW, an invalid state exists

d)

The input is toggled into the flip-flop on the leading edge of the clock and is passed to the output on the trailing edge of the clock

| | Ishan Saini answered |

Operation of Positive Edge-Triggered D Flip-Flop

The positive edge-triggered D flip-flop is a type of sequential logic circuit that stores one bit of data. It has a single input called D (data) and two outputs called Q (output) and Q' (complementary output). The operation of the positive edge-triggered D flip-flop is as follows:

Leading Edge of the Clock

On the leading edge of the clock, the input D is sampled and stored in the flip-flop. The output Q reflects the value of the input D at the time of the leading edge of the clock. The output Q' is the complement of the output Q.

Trailing Edge of the Clock

On the trailing edge of the clock, the output Q remains stable and retains its previous value. The output Q' also remains stable and retains its previous complemented value.

Advantages of Positive Edge-Triggered D Flip-Flop

The positive edge-triggered D flip-flop has the following advantages:

- It is immune to glitches and noise on the input D during the clock transition.

- It has a predictable and reliable timing behavior.

- It can be easily cascaded to build more complex sequential circuits.

Conclusion

The positive edge-triggered D flip-flop is a fundamental building block of digital circuits. It provides a simple and reliable way to store one bit of data and synchronize it with a clock signal. Its operation on the leading and trailing edges of the clock makes it suitable for a wide range of applications, such as registers, counters, and state machines.

The positive edge-triggered D flip-flop is a type of sequential logic circuit that stores one bit of data. It has a single input called D (data) and two outputs called Q (output) and Q' (complementary output). The operation of the positive edge-triggered D flip-flop is as follows:

Leading Edge of the Clock

On the leading edge of the clock, the input D is sampled and stored in the flip-flop. The output Q reflects the value of the input D at the time of the leading edge of the clock. The output Q' is the complement of the output Q.

Trailing Edge of the Clock

On the trailing edge of the clock, the output Q remains stable and retains its previous value. The output Q' also remains stable and retains its previous complemented value.

Advantages of Positive Edge-Triggered D Flip-Flop

The positive edge-triggered D flip-flop has the following advantages:

- It is immune to glitches and noise on the input D during the clock transition.

- It has a predictable and reliable timing behavior.

- It can be easily cascaded to build more complex sequential circuits.

Conclusion

The positive edge-triggered D flip-flop is a fundamental building block of digital circuits. It provides a simple and reliable way to store one bit of data and synchronize it with a clock signal. Its operation on the leading and trailing edges of the clock makes it suitable for a wide range of applications, such as registers, counters, and state machines.

Propagation delay of flip flops used for counter design largely affects the speed of operation of- a)asynchronous (ripple) counter

- b)synchronous up counter

- c)synchronous down counter

- d)synchronous up down counter

Correct answer is option 'A'. Can you explain this answer?

Propagation delay of flip flops used for counter design largely affects the speed of operation of

a)

asynchronous (ripple) counter

b)

synchronous up counter

c)

synchronous down counter

d)

synchronous up down counter

| | Kiran Iyer answered |

Propagation delay is the time it takes for a signal to propagate through a logic gate or flip flop. In the context of counter design, the propagation delay of flip flops plays a significant role in determining the speed of operation, especially in asynchronous (ripple) counters.

Asynchronous counters are designed using a series of flip flops, where the output of one flip flop serves as the clock input for the next flip flop in the chain. Each flip flop introduces a certain amount of propagation delay, which is the time it takes for the output of the flip flop to stabilize after a change in its inputs.