GATE Exam > GATE Questions > For a given sample-and-hold circuit, if the v...

Start Learning for Free

For a given sample-and-hold circuit, if the value of the hold capacitor is increased, then

- a)droop rate decreases and acquisition time decreases

- b)droop rate decreases and acquisition time increases

- c)droop rate increases and acquisition time decreases

- d)droop rate increases and acquisition time increases

Correct answer is option 'B'. Can you explain this answer?

| FREE This question is part of | Download PDF Attempt this Test |

Most Upvoted Answer

For a given sample-and-hold circuit, if the value of the hold capacito...

Explanation:

A sample-and-hold circuit is an electronic circuit used to capture an analog signal and hold its value. It consists of a switch, a capacitor, and an amplifier. The switch is used to sample the input signal and charge the capacitor, and then it is opened to hold the voltage across the capacitor.

Droop Rate:

Droop rate is the rate at which the voltage across the capacitor decreases over time. It is caused by leakage current and parasitic resistance. A higher droop rate means that the capacitor discharges faster and the hold time is shorter.

Acquisition Time:

Acquisition time is the time required for the capacitor to charge to the full value of the input signal. A shorter acquisition time means that the circuit can capture the input signal more quickly.

Effect of Increasing the Hold Capacitor:

When the hold capacitor is increased, the following effects occur:

- Droop rate decreases: As the capacitance increases, the capacitor can hold more charge, and the voltage across it decreases more slowly. Therefore, the droop rate decreases.

- Acquisition time increases: As the capacitance increases, it takes longer for the capacitor to charge to the full value of the input signal. Therefore, the acquisition time increases.

Therefore, the correct answer is option 'B' - droop rate decreases and acquisition time increases.

A sample-and-hold circuit is an electronic circuit used to capture an analog signal and hold its value. It consists of a switch, a capacitor, and an amplifier. The switch is used to sample the input signal and charge the capacitor, and then it is opened to hold the voltage across the capacitor.

Droop Rate:

Droop rate is the rate at which the voltage across the capacitor decreases over time. It is caused by leakage current and parasitic resistance. A higher droop rate means that the capacitor discharges faster and the hold time is shorter.

Acquisition Time:

Acquisition time is the time required for the capacitor to charge to the full value of the input signal. A shorter acquisition time means that the circuit can capture the input signal more quickly.

Effect of Increasing the Hold Capacitor:

When the hold capacitor is increased, the following effects occur:

- Droop rate decreases: As the capacitance increases, the capacitor can hold more charge, and the voltage across it decreases more slowly. Therefore, the droop rate decreases.

- Acquisition time increases: As the capacitance increases, it takes longer for the capacitor to charge to the full value of the input signal. Therefore, the acquisition time increases.

Therefore, the correct answer is option 'B' - droop rate decreases and acquisition time increases.

Free Test

FREE

| Start Free Test |

Community Answer

For a given sample-and-hold circuit, if the value of the hold capacito...

Concepts:

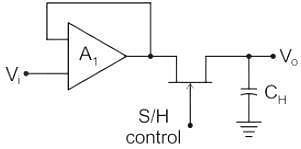

Generally, a sample & hold circuit is designed using an opamp. The given circuit shows the general implementation:

Sample & Hold circuit capacitor CH is charged by the AmplifierA1.

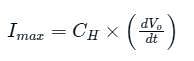

The maximum output current of the opamp is given as:

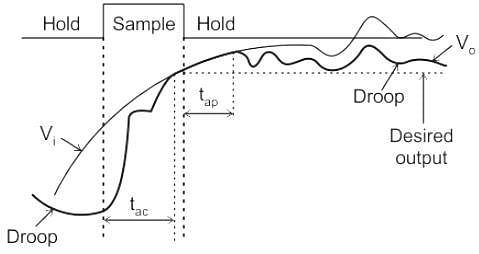

Droop rate = dVo/dt, when V0 is the voltage at the steady state.

The acquisition time (tac) is depicted in the following figure:

|

Explore Courses for GATE exam

|

|

Similar GATE Doubts

For a given sample-and-hold circuit, if the value of the hold capacitor is increased, thena)droop rate decreases and acquisition time decreasesb)droop rate decreases and acquisition time increasesc)droop rate increases and acquisition time decreasesd)droop rate increases and acquisition time increasesCorrect answer is option 'B'. Can you explain this answer?

Question Description

For a given sample-and-hold circuit, if the value of the hold capacitor is increased, thena)droop rate decreases and acquisition time decreasesb)droop rate decreases and acquisition time increasesc)droop rate increases and acquisition time decreasesd)droop rate increases and acquisition time increasesCorrect answer is option 'B'. Can you explain this answer? for GATE 2024 is part of GATE preparation. The Question and answers have been prepared according to the GATE exam syllabus. Information about For a given sample-and-hold circuit, if the value of the hold capacitor is increased, thena)droop rate decreases and acquisition time decreasesb)droop rate decreases and acquisition time increasesc)droop rate increases and acquisition time decreasesd)droop rate increases and acquisition time increasesCorrect answer is option 'B'. Can you explain this answer? covers all topics & solutions for GATE 2024 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for For a given sample-and-hold circuit, if the value of the hold capacitor is increased, thena)droop rate decreases and acquisition time decreasesb)droop rate decreases and acquisition time increasesc)droop rate increases and acquisition time decreasesd)droop rate increases and acquisition time increasesCorrect answer is option 'B'. Can you explain this answer?.

For a given sample-and-hold circuit, if the value of the hold capacitor is increased, thena)droop rate decreases and acquisition time decreasesb)droop rate decreases and acquisition time increasesc)droop rate increases and acquisition time decreasesd)droop rate increases and acquisition time increasesCorrect answer is option 'B'. Can you explain this answer? for GATE 2024 is part of GATE preparation. The Question and answers have been prepared according to the GATE exam syllabus. Information about For a given sample-and-hold circuit, if the value of the hold capacitor is increased, thena)droop rate decreases and acquisition time decreasesb)droop rate decreases and acquisition time increasesc)droop rate increases and acquisition time decreasesd)droop rate increases and acquisition time increasesCorrect answer is option 'B'. Can you explain this answer? covers all topics & solutions for GATE 2024 Exam. Find important definitions, questions, meanings, examples, exercises and tests below for For a given sample-and-hold circuit, if the value of the hold capacitor is increased, thena)droop rate decreases and acquisition time decreasesb)droop rate decreases and acquisition time increasesc)droop rate increases and acquisition time decreasesd)droop rate increases and acquisition time increasesCorrect answer is option 'B'. Can you explain this answer?.

Solutions for For a given sample-and-hold circuit, if the value of the hold capacitor is increased, thena)droop rate decreases and acquisition time decreasesb)droop rate decreases and acquisition time increasesc)droop rate increases and acquisition time decreasesd)droop rate increases and acquisition time increasesCorrect answer is option 'B'. Can you explain this answer? in English & in Hindi are available as part of our courses for GATE.

Download more important topics, notes, lectures and mock test series for GATE Exam by signing up for free.

Here you can find the meaning of For a given sample-and-hold circuit, if the value of the hold capacitor is increased, thena)droop rate decreases and acquisition time decreasesb)droop rate decreases and acquisition time increasesc)droop rate increases and acquisition time decreasesd)droop rate increases and acquisition time increasesCorrect answer is option 'B'. Can you explain this answer? defined & explained in the simplest way possible. Besides giving the explanation of

For a given sample-and-hold circuit, if the value of the hold capacitor is increased, thena)droop rate decreases and acquisition time decreasesb)droop rate decreases and acquisition time increasesc)droop rate increases and acquisition time decreasesd)droop rate increases and acquisition time increasesCorrect answer is option 'B'. Can you explain this answer?, a detailed solution for For a given sample-and-hold circuit, if the value of the hold capacitor is increased, thena)droop rate decreases and acquisition time decreasesb)droop rate decreases and acquisition time increasesc)droop rate increases and acquisition time decreasesd)droop rate increases and acquisition time increasesCorrect answer is option 'B'. Can you explain this answer? has been provided alongside types of For a given sample-and-hold circuit, if the value of the hold capacitor is increased, thena)droop rate decreases and acquisition time decreasesb)droop rate decreases and acquisition time increasesc)droop rate increases and acquisition time decreasesd)droop rate increases and acquisition time increasesCorrect answer is option 'B'. Can you explain this answer? theory, EduRev gives you an

ample number of questions to practice For a given sample-and-hold circuit, if the value of the hold capacitor is increased, thena)droop rate decreases and acquisition time decreasesb)droop rate decreases and acquisition time increasesc)droop rate increases and acquisition time decreasesd)droop rate increases and acquisition time increasesCorrect answer is option 'B'. Can you explain this answer? tests, examples and also practice GATE tests.

|

Explore Courses for GATE exam

|

|

Suggested Free Tests

Signup for Free!

Signup to see your scores go up within 7 days! Learn & Practice with 1000+ FREE Notes, Videos & Tests.